# Impact of Power-Supply Noise on Phase Noise Performance of RF DACs

Fanlong Li

Data Converters — Wireless Infrastructure

#### **ABSTRACT**

This application report examines the impact of power-supply noise on an on-chip sampling clock, and consequently, on the output performance of a radio-frequency (RF) digital-to-analog converter (DAC). Through theoretical analysis and practical measurement using TI's RF DAC devices, the DAC38RF8x and DAC38RF9x, this article gives the quantized requirement for the power supply, and provides an efficient and direct guide for DAC applications.

|   | Contents                                                                                                                      |   |

|---|-------------------------------------------------------------------------------------------------------------------------------|---|

| 1 | Introduction                                                                                                                  | 2 |

| 2 | Theoretical Analysis                                                                                                          | 3 |

| 3 | Practical Measurement of Increasing the PLL Loop Bandwidth and Using a Better VCO Power Supply                                | 4 |

| 4 | Summary                                                                                                                       | 7 |

| 5 | References                                                                                                                    | 7 |

|   | List of Figures                                                                                                               |   |

| 1 | IF DAC Solution Versus RF DAC Integrated Solution                                                                             | 2 |

| 2 | Typical Block Diagram of the PLL and the PLL Transfer Function                                                                | 3 |

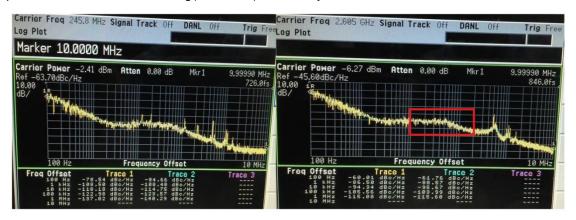

| 3 | PLL Reference Clock Phase Noise (Left), and Abnormal DAC Output Phase Noise at 2605 MHz at 200-kHz PLL Loop Bandwidth (Right) | 2 |

| 4 | Signal EVM With the Phase Noise From                                                                                          | 5 |

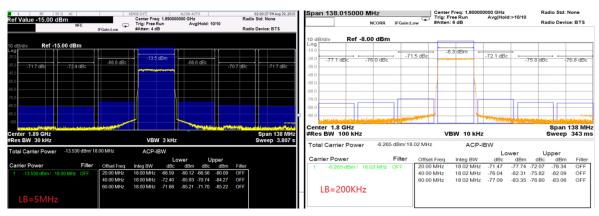

| 5 | PLL Reference Clock Phase Noise (Left), and Normal DAC Output Phase Noise at 2605 MHz at 5-MHz PLL Loop Bandwidth (Right)     | 5 |

| 6 | Signal EVM With the Phase Noise From                                                                                          | 6 |

| 7 | ACPR With 5-MHz PLL Loop Bandwidth (Left), and ACPR With 200-kHz PLL Loop Bandwidth (Right)                                   | 6 |

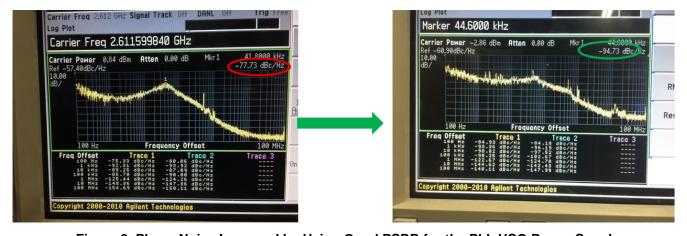

| 8 | Phase Noise Improved by Using Good PSRR for the PLL VCO Power Supply                                                          | 6 |

|   | List of Tables                                                                                                                |   |

| 1 | Comparison Between PLL Input and Output Phase Noise With Narrow Loop Bandwidth                                                | 5 |

| 2 | Comparison Between PLL Input and Output Phase Noise With Wide Loop Bandwidth                                                  |   |

#### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

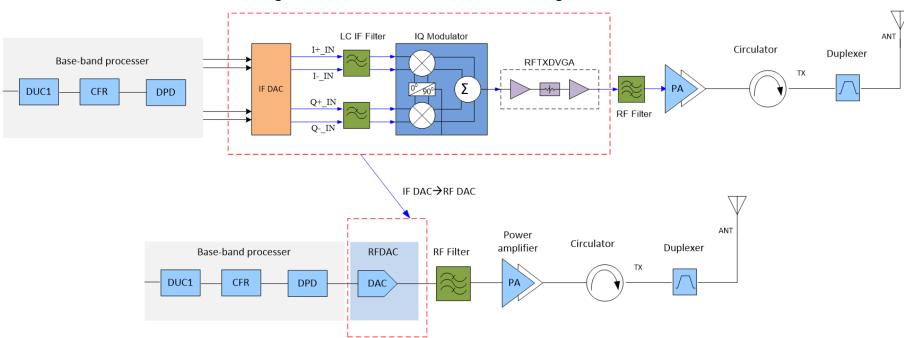

The digital-to-analog converter (DAC) is a key device component in modern wireless communication products, and DAC performance dominates the entire transmit signal path in the radio remote unit (RRU). Along with the development of advanced IC technology, RF-sampling DACs can directly sample at the RF frequency. Figure 1 shows how compared to an intermediate-frequency (IF) sampling DAC, an RF DAC gives the system designer a better integration solution with fewer components, and achieves a software-defined radio to give the designer more flexibility. RF DACs are gaining wide popularity in fourth generation (4G) wireless systems, such as the macro FDD and TDD systems.

Figure 1. IF DAC Solution Versus RF DAC Integrated Solution

www.ti.com Theoretical Analysis

## 2 Theoretical Analysis

In this section, we discuss how the quality of power supply affects the phased-locked loop (PLL) output phase noise through basic PLL theory analysis.

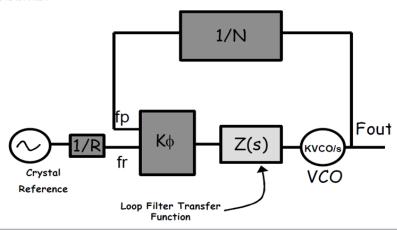

Figure 2 shows a typical block diagram of the PLL, and the PLL transfer function.

#### **PLL Basic Structure**

$$G_{CL}(s) = \frac{G(s)}{1 + G(s) * H(s)}$$

when  $s \to 0$ ,  $G_{CL}(s) \to 1/H(s)$ ; when  $s \to \infty$ ,  $G_{CL}(s) \to 0$  Low Pass For Ref PN

Figure 2. Typical Block Diagram of the PLL and the PLL Transfer Function

Figure 2 shows the typical block diagram of PLL, and the PLL noise transfer function. The  $\omega$  denotes the PLL loop bandwidth. Based on the PLL transfer function, noise injected in the voltage-controlled oscillator (VCO) passes high-pass filtering at the PLL output, whereas noise injected in other parts passes low-pass filtering.

Based on the two types of PLL transfer functions, the PLL power-supply noise is divided into two related components: the VCO power supply noise and the non-VCO power-supply noise.

Power-supply noise is usually lower-frequency noise (< 1 MHz), so it is easily understood that non-VCO power-supply noise impacts the PLL phase noise because of the low-pass filter characteristics. On the other hand, VCO power-supply noise can be ignored because VCO power-supply noise has high-pass filter characteristics, and thus filters the low-frequency noise. Take extra care here because there is no absolute high-pass or low-pass filter; the VCO filter suppression depends on the PLL loop bandwidth setting. The PLL loop bandwidth controls the transition zone range. Therefore, if the loop bandwidth is

narrow (for example, 100 kHz), then the transition zone of the VCO transfer function is also very narrow, and there is almost no suppression for low-frequency power-supply noise. In such cases, the VCO power-supply low-frequency noise impacts on the PLL output directly. In a real application, always remember to choose a low-noise power supply for the non-VCO power design, but ignore the VCO power noise. This application report focuses on the analysis of VCO power supply noise impact on the PLL phase noise.

Based on the previous analysis, the following two methods improve the VCO power supply noise suppression:

- Increase the PLL loop bandwidth. The VCO noise transfer function is a high-pass type; therefore, when

the loop bandwidth increases, the transition zone range increases as well, and low-frequency

suppression is stronger. In that sense, the low-frequency noise of power supply must be well

suppressed.

- Choose a good PSRR for the VCO power supply. Good VCO PSRR is also able to do a good job of suppressing the close-in phase noise.

# 3 Practical Measurement of Increasing the PLL Loop Bandwidth and Using a Better VCO Power Supply

In order to demonstrate the VCO power-supply noise impact on the PLL output phase noise, use a power supply with bad noise at 10 kHz offset, and assume a PSRR of 35 dB at 10 kHz. The following measurement shows the power noise effect at both a narrow and wide PLL loop bandwidth.

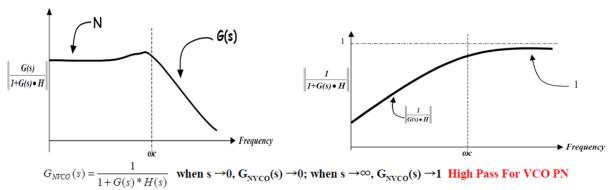

First, a narrow loop bandwidth measurement is performed. The internal PLL of the RF DAC multiplies the external reference clock (245.76 MHz) by 36 to 8847.36 MHz. The PLL loop bandwidth is set to 200 kHz and the phase noise of DAC can be observed when generating an output CW tone at 2605 MHz using the internal digital NCO, as shown in Figure 3.

Figure 3. PLL Reference Clock Phase Noise (Left), and Abnormal DAC Output Phase Noise at 2605 MHz at 200-kHz PLL Loop Bandwidth (Right)

The phase noise plot on the left of Figure 3 shows the external reference clock 245.76 MHz. The plot on right side is the phase noise of CW tone at 2605 MHz. The DAC output CW-tone phase noise is used to represent the internal PLL/VCO performance. According to the basic theory of PLL, inside the PLL loop bandwidth, the PLL output phase noise is dominated by the reference input phase noise, and the in-band phase noise of PLL output is a scaled version of reference input by 20log(Fout / Fin). In this example, Fin is 245.76 MHz and Fout is 2605 MHz; therefore, the close-in (< 200-kHz offset) output phase noise is from the corresponding reference clock noise scaled up by 20.5 dB (20log(2605 / 245.76)). Table 1 shows that the phase noise from 10 kHz to 100 kHz deviates a lot from the expected number in theory, which is degraded compared to 20log(Fout / Fin) curve, and shows an obvious hump at around the 10-kHz offset (highlight in the red square).

Table 1. Comparison Between PLL Input and Output Phase Noise With Narrow Loop Bandwidth

| Input R | leference Clock | Out     | Delta Number |          |  |

|---------|-----------------|---------|--------------|----------|--|

| Offset  | Phase Noise     | Offset  | Phase Noise  | Pout-Pin |  |

| 100 Hz  | -78 dBc/Hz      | 100 Hz  | -58 dBc/Hz   | 20 dB    |  |

| 1 kHz   | -104 dBc/Hz     | 1 kHz   | -83 dBc/Hz   | 21 dB    |  |

| 10 kHz  | -121 dBc/Hz     | 10 kHz  | -85 dBc/Hz   | 36 dB    |  |

| 100 kHz | -121 dBc/Hz     | 100 kHz | -87 dBc/Hz   | 34 dB    |  |

The close-in phase noise degradation at the DAC output degrades the in-band signal quality, and thus system transmit performance. By calculating integrated jitter from phase-noise measurement plot, the error vector magnitude (EVM) is degraded to ~6%, as shown in Figure 4, and does not meet the customer requirement of 3%.

| 100HZ | 1KHZ | 10KHZ | 100KHZ | 1MHZ | Jitter1    | Jitter2  | Jitter3  | Jitter4 | Jitter total | EVM  |

|-------|------|-------|--------|------|------------|----------|----------|---------|--------------|------|

|       |      |       |        |      |            |          |          |         |              |      |

| -58   | -83  | -85   | -87    | -121 | -31.454163 | -44.3434 | -36.3434 | -30.47  | 0.001883     | 6.14 |

Figure 4. Signal EVM With the Phase Noise From Table 1

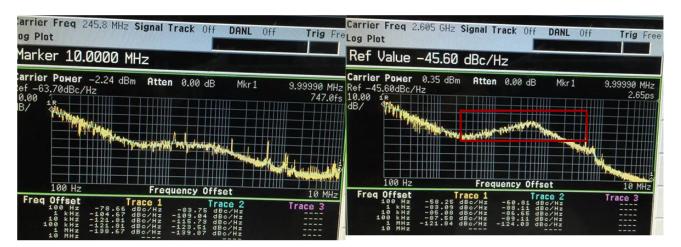

The same measurement is repeated, increasing the PLL loop bandwidth from 200 kHz to 5 MHz, as shown in Figure 5. Now there is no obvious bump around the 10-kHz offset. Table 2 shows that the close in phase noise matches the 20log(Fout / Fin) curve very well.

Figure 5. PLL Reference Clock Phase Noise (Left), and Normal DAC Output Phase Noise at 2605 MHz at 5-MHz PLL Loop Bandwidth (Right)

Table 2. Comparison Between PLL Input and Output Phase Noise With Wide Loop Bandwidth

| Input F | Reference Clock | Out     | Delta Number |          |  |

|---------|-----------------|---------|--------------|----------|--|

| Offset  | Phase Noise     | Offset  | Phase Noise  | Pout-Pin |  |

| 100 Hz  | -84 dBc/Hz      | 100 Hz  | -61 dBc/Hz   | 23 dB    |  |

| 1 kHz   | -108 dBc/Hz     | 1 kHz   | -88 dBc/Hz   | 20 dB    |  |

| 10 kHz  | -114 dBc/Hz     | 10 kHz  | -95 dBc/Hz   | 19 dB    |  |

| 100 kHz | -123 dBc/Hz     | 100 kHz | -103 dBc/Hz  | 20 dB    |  |

The close-in phase noise degradation at the DAC output degrades the in-band signal quality. By calculating integrated jitter from phase noise measurement plot, the EVM is improved to ~3%, as shown in Figure 6, and meets the customer requirement of 3%.

| 100HZ | 1KHZ | 10KHZ | 100KHZ | 1MHZ | Jitter1    | Jitter2  | Jitter3 | Jitter4 | Jitter total | EVM  |

|-------|------|-------|--------|------|------------|----------|---------|---------|--------------|------|

|       |      |       |        |      |            |          |         |         |              |      |

| -61   | -88  | -95   | -103   | -115 | -34.459218 | -50.6778 | -47.829 | -46.20  | 0.000407     | 2.85 |

Figure 6. Signal EVM With the Phase Noise From Table 2.

Furthermore, by using a larger loop bandwidth, the DAC output signal adjacent channel power ratio (ACPR) is degraded. By changing from a 200k to a 5M loop bandwidth; the ACPR degrades from 71 dBc to 66 dBc, as shown in Figure 7. Therefore, in wireless communication products, a larger loop bandwidth cannot be used; usually, the ACPR must achieve 70 dBc.

Figure 7. ACPR With 5-MHz PLL Loop Bandwidth (Left), and ACPR With 200-kHz PLL Loop Bandwidth (Right)

Practical measurement of using better power supply also had been done. Compared with PSRR of 35 dB at a 10-kHz power supply, a comparison measurement is done by using TI's TSP7A84 LDO that has a PSRR at 10-kHz offset of 57 dB, as shown in Figure 8 (right). Now the DAC output phase noise at 10-kHz offset is significantly improved from -77 dBc to -94 dBc; a 17-dB improvement.

Figure 8. Phase Noise Improved by Using Good PSRR for the PLL VCO Power Supply

In order to get the good EVM and ACPR of an RF DAC output signal, choose a good performance LDO. In this case, TI's TPS7A84 allows the system to achieve EVM (1.35%) and ACPR (71 dBc) at 2.6-G RF DAC output.

www.ti.com Summary

## 4 Summary

The wireless system has a relatively tight requirement for TX ACPR performance, so good ACPR performance is achieved by using a narrow PLL loop bandwidth. In that sense, make sure to get good power-supply performance for the PLL. From the practical measurement conducted in this application report, the PLL VCO power supply must have a PSRR specified > 50-dB at 10 kHz, and power-supply noise must be < 10  $\mu$ V. The guidance to design a power supply for an RF DAC using the 3-A TPS7A84 LDO provides overall greater system performance.

#### 5 References

- Texas Instruments, DAC38RFxx Dual- or Single-Channel, Single-Ended or Differential Output, 14-Bit, 9-GSPS, RF-Sampling DAC With JESD204B Interface and On-Chip PLL Data Sheet

- Texas Instruments, TPS7A84 High-Current (3 A), High-Accuracy (1%), Low-Noise (4.4 μVRMS), LDO Voltage Regulator Data Sheet

- Dean Banerjee (2001). PLL Performance, Simulation, and Design, Second Edition

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated