# Extracting Maximum Power from an Adapter with Input Current Optimization Feature

BCP SCS

#### **ABSTRACT**

To maximize the output power of any adaptor that charges a battery, some battery chargers include the input current optimization (ICO) feature. This application note explains how the ICO feature configures the current limit of the charger input to the maximum allowed without overloading the power source of the charger.

|   | Contents                                                                                |   |  |  |  |  |  |  |

|---|-----------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

| 1 | Background                                                                              | 1 |  |  |  |  |  |  |

| 2 | Operation                                                                               | 2 |  |  |  |  |  |  |

| 3 | BackgroundOperationSummary                                                              | 5 |  |  |  |  |  |  |

|   | List of Figures                                                                         |   |  |  |  |  |  |  |

| 1 | Effective Input Current Limit Set by V <sub>INDPM</sub>                                 | 2 |  |  |  |  |  |  |

| 2 | Graphical Representation of ICO During Operation                                        | 3 |  |  |  |  |  |  |

| 3 | Automatic ICO Detection After Charge Current Increase With V(BAT) > V <sub>MINSYS</sub> | 3 |  |  |  |  |  |  |

| 4 | Automatic ICO Detection After Charge Current Increase With V(BAT) < V <sub>MINSYS</sub> | 3 |  |  |  |  |  |  |

| 5 | Forced ICO Detection With $V(BAT) > V_{MINSYS}$                                         | 4 |  |  |  |  |  |  |

|   | List of Tables                                                                          |   |  |  |  |  |  |  |

| 1 | Battery Charge ICs With ICO and Relevant Bits                                           | 4 |  |  |  |  |  |  |

| 2 | Example Current Limit Register Results                                                  | 5 |  |  |  |  |  |  |

#### **Trademarks**

All trademarks are the property of their respective owners.

#### 1 Background

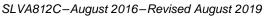

Wall adapters that power portable electronic devices come in a variety of voltage and current ratings. Most battery chargers inside these portable devices include one or more fast-response feedback control loops. These prevent the charger from pulling too much current from the wall adapter, which collapses it. One such loop is the input current-limit dynamic power management ( $I_{\text{INDPM}}$ ) loop. The designer, through an external resistor, I2C register, or the D+/D- circuitry of the charger, automatically sets a predetermined value for the amount of input current the charger is allowed to pull from the adapter. The dynamic power-path management circuitry of the charger then distributes this input power to the system load and uncharged battery, reducing charge current if necessary, to provide the demanded DC, or transient system load. In the event the adapter cannot provide the rated output current, or because of highly resistive connections from the source to the charger, the charger input pin voltage droops. This can also happen when an adapter unknown to D+/D- detection (for example, a third-party adapter) is attached, and the charger sets the  $I_{\text{INDPM}}$  setting too high. When this happens, the second feedback loop, input voltage dynamic power management ( $V_{\text{INDPM}}$ ), activates. As highlighted in Figure 1, this reduces the charge current to prevent the charger from crashing the adapter.

Operation www.ti.com

Figure 1. Effective Input Current Limit Set by VINDPM

At start-up, the charger sets a default  $V_{\text{INDPM}}$  threshold (for example, the BQ25890 sets  $V_{\text{INDPM}(TH)}$  to 600 mV below the unloaded input voltage). The host software can change the desired input current limit, or  $V_{\text{INDPM}}$  voltage thresholds, via I2C anytime. If the input voltage droop is due to highly resistive connections, allowing the  $V_{\text{INDPM}}$  loop of the charger to continuously control and regulate the charger input voltage, therefore preventing further droop, is acceptable. If, however, the droop is due to an adapter overload, reducing the input current limit of the charger to a level at which the adapter is not in overload is preferable. More details about  $I_{\text{INDPM}}$  and  $V_{\text{INDPM}}$  can be found in the Dynamic Power-Path Mgmt & Dynamic Power Mgmt Application Report.

The ICO circuitry identifies and sets the maximum (optimal) current the charger can pull from the adapter without collapsing the adapter.

## 2 Operation

The actual input-current limit is the lower value set by the ILIM pin resistor, or as reported by the input current limit register bits, unless the host-controlled EN\_ILIM bit of the charger is disabled. In other words, the ILIM pin resistor clamps the maximum input current limit value. The remainder of the application note assumes that the host-controlled EN\_ILIM = 0 of the charger, or that the ILIM resistor is set higher than the ICO determined current limit. This results in the ICO input current limit register reporting the actual input current limit in use.

When ICO is disabled, or until the ICO algorithm has optimized the input current limit, the ICO status bits indicate that optimization is disabled, in progress, or complete. The ICO-optimized input current register reports the same value as configured in the input current limit register by the D+/D- algorithm, the PSEL pin at start-up, or the host software.

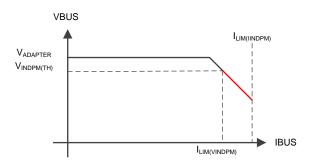

If ICO is enabled, the charger waits for the first  $V_{\text{INDPM}}$  event to occur. This is the desired system, plus charge current power, to exceed the output power capability of the power source. It reports, per the ICO status bits, that ICO optimization is in progress. When  $V(\text{BAT}) > V_{\text{MINSYS}}$  and a  $V_{\text{INDPM}}$  event occurs, the ICO algorithm does the following:

- 1. Reduces the input current limit register, and the charger maximum allowed input current, to 500 mA

- 2. Steps up the current limit until the input voltage drops to the V<sub>INDPM</sub> threshold

- 3. Lowers the input current limit register slightly below the point where VINDPM is reached

- 4. Updates the ICO input current limit register to this input current limit value

- 5. Updates the ICO status bits

Figure 2 is a graphical representation of the ICO algorithm list discussed previously. It is assumed that the system load, or charge current, increases at the point where the VBUS voltage is no longer at the adapter voltage (V<sub>ADPTR</sub>).

www.ti.com Operation

Figure 2. Graphical Representation of ICO During Operation

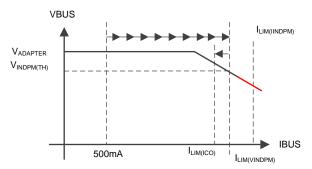

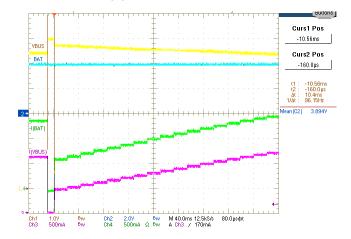

Figure 3 is a scope shot of the BQ25890 ICO circuitry, on a board with a 0.5- $\Omega$  input resistance from a 6-V supply, and a 5.3-V V<sub>INDPM</sub> threshold. The charge current increases from 1 A to 4 A, causing the input voltage to droop to V<sub>INDPM</sub> and trigger an ICO.

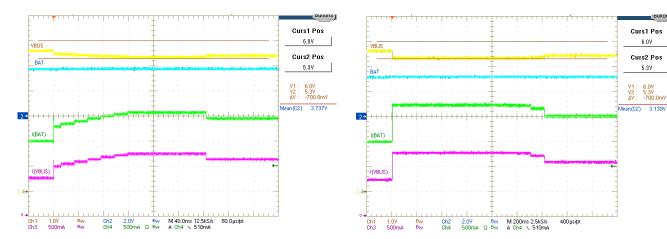

When  $V(BAT) < V_{MINSYS}$ , the battery voltage can be too low to supplement a large system load if the charger buck converter is limited to 500 mA, then ramped up by the ICO algorithm. Therefore, when a  $V(BAT) < V_{MINSYS}$  and a  $V_{INDPM}$  event occurs, the ICO algorithm works by:

- 1. Setting the input current equal to the input current-limit register value (which is clamped to a lower value by the V<sub>INDPM</sub> control loop)

- 2. Stepping down the current limit until the charger exits V<sub>INDPM</sub> control

- 3. Updating the ICO input current-limit register to this input current-limit value

- 4. Updating the ICO status bits

Figure 4 is a scope shot of the same BQ25890 board, but with a  $V(BAT) < V_{MINSYS}$ .

The input current limit remains optimized, and does not automatically run the ICO detection algorithm again, unless the following occurs:

- Another V<sub>INDPM</sub> event

- · Input current-limit register changes

- V<sub>INDPM</sub> offset or the absolute V<sub>INDPM</sub> registers changes

- Force V<sub>INDPM</sub> register changes

Additionally, if a DCP or HVDCP adapter is detected at start up by the D+/D- circuitry, the ICO algorithm automatically runs.

Figure 3. Automatic ICO Detection After Charge Current Increase With  $V(BAT) > V_{MINSYS}$

Figure 4. Automatic ICO Detection After Charge Current Increase With V(BAT) < V<sub>MINSYS</sub>

Operation www.ti.com

The host software can also force ICO detection using the FORCE\_ICO bit, or by toggling the ICO enable bit (which defaults to 1). As shown in Figure 5, when forcing detection in the BQ25890, the ICO detection algorithm first disables charge for 10 ms. Then, it applies a 10 mA sink on the BAT to determine whether V(BAT) is greater than or equal to  $V_{\text{MINSYS}}$ , and proceeds as previously described.

Figure 5. Forced ICO Detection With V(BAT) > V<sub>MINSYS</sub>

shows which battery chargers have ICO, the relevant I2C registers for the host-controlled chargers, and how ICO is activated.

Table 1. Battery Charge ICs With ICO and Relevant Bits

| Charger                                              | Desired<br>Input<br>Current-<br>Limit<br>Register<br>Bits | EN_ILIM<br>Pin<br>Register<br>Bit | ICO-Enable<br>Bit | Input Current-<br>Limit When ICO<br>Active Bits<br>Register | ICO Status<br>Bits | Force ICO Bit | V <sub>INDPM</sub> Register<br>Bits | How/When Activated <sup>(1)</sup>                                                                                                                                                                                                                                                |

|------------------------------------------------------|-----------------------------------------------------------|-----------------------------------|-------------------|-------------------------------------------------------------|--------------------|---------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BQ25890<br>BQ25892<br>BQ25895<br>BQ25896<br>BQ25895M | REG00[0:5]                                                | REG00[6]                          | REG02[4]          | REG13[0:5]                                                  | REG14[6]           | REG09[7]      | REG01[0:4]<br>REG0D                 | Immediately following DCP source detection if enable ICO bit = 1. If DCF input source detected, enable ICO set to 1, EN_HIZ bit toggled, IINDPM register changed, V <sub>INDPM</sub> register changed, V <sub>INDPM</sub> event; Force ICO set to 1 even if not DCP input source |

| BQ25890H<br>BQ25898<br>BQ25898D                      | REG00[0:5]                                                | REG00[6]                          | REG02[4]          | REG13[0:5]                                                  | REG14[6]           | REG09[7]      | REG01[0]<br>REG0D                   |                                                                                                                                                                                                                                                                                  |

| BQ25882<br>BQ25883<br>BQ25887                        | REG03[0:4]                                                | REG01[6]                          | REG03[5]          | REG0A[0:4]                                                  | REG0C[1:2]         | REG03[7]      | REG02[0:4]                          | Same as above plus VBUS OVP event                                                                                                                                                                                                                                                |

| BQ25886                                              | N/A                                                       | N/A                               | N/A               | N/A                                                         | N/A                | N/A           | N/A                                 | Only if and immediately following DCP detection by D+/D- algoirthm or if DCP and V <sub>INDPM</sub> event                                                                                                                                                                        |

<sup>(1)</sup> Even if activated, ICO may not complete (no input current limit reduction) if SYS + BAT load is not high enough to cause V<sub>INDPM</sub> event during input current limit sweep

Table 2 summarizes possible cases for input current limit registers for the BQ25890.

www.ti.com Summary

#### **Table 2. Example Current Limit Register Results**

|              | TEST                                                | CONDITIONS                      | RESULTS       |                                       |                                                                       |                                   |  |  |  |

|--------------|-----------------------------------------------------|---------------------------------|---------------|---------------------------------------|-----------------------------------------------------------------------|-----------------------------------|--|--|--|

| Adapter      | Max Input Current<br>Limit per ILIM Pin<br>Resistor | Input Current-Limit<br>Register | ICHG Register | ILIM When ICO<br>Active Bits Register | ICO Status Register                                                   | Actual Input<br>Current Limit     |  |  |  |

|              | Case 1                                              |                                 |               |                                       |                                                                       |                                   |  |  |  |

| 5 V at 3 A   | 2 A                                                 | 3.25 A                          | 5 A           | 3.25 A                                | 1                                                                     | 2 A – clamped by<br>ILIM resistor |  |  |  |

|              |                                                     |                                 | Case 2        |                                       |                                                                       |                                   |  |  |  |

| 5 V at 1.5 A | 2 A                                                 | 3.25 A                          | 5 A           | 1.5 A                                 | 1                                                                     | 1.5 A – ICO finds optimal setting |  |  |  |

| Case 3       |                                                     |                                 |               |                                       |                                                                       |                                   |  |  |  |

| 5 V at 3 A   | 3 A                                                 | 2 A                             | 5 A           | 2 A                                   | 1                                                                     | 2 A – clamped to<br>INLIM         |  |  |  |

| Case 4       |                                                     |                                 |               |                                       |                                                                       |                                   |  |  |  |

| 5 V at 3 A   | 3 A                                                 | 3.25 A                          | 2 A           | 3.25 A                                | 0 – ICO in progress<br>because ICHG does not<br>require IBUS = 3.25 A | 3 A                               |  |  |  |

### 3 Summary

The  $V_{\text{INDPM}}$  loop of a charger is the last line of defense in preventing the charger from collapsing the input source (for example, the adapter). While the charger is fully capable of indefinitely regulating the input current limit using the  $V_{\text{INDPM}}$  loop, running a wall adapter in an overload state is unhealthy for the adapter. The designer sets the input current limit, either through an external ILIM resistor or input current limit I<sup>2</sup>C register, to match the adapter-rated current. In the event of malfunctioning adapters, or highly resistive adapter cables, the ICO circuitry of the battery charger finds the optimal input current-limit setting of the charger for the maximum power extraction without adapter overload.

Revision History www.ti.com

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | Changes from B Revision (July 2019) to C Revision                                               |   |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------|---|--|--|--|--|

| •  | Updated abstract                                                                                |   |  |  |  |  |

|    | Edited application report for clarity                                                           |   |  |  |  |  |

| •  | Updated Section 1                                                                               | 1 |  |  |  |  |

| •  | Updated Section 2                                                                               | 2 |  |  |  |  |

| •  | Deleted BQ2589X family register addresses from body of text and added BQ2588X family in Table 1 | 4 |  |  |  |  |

|    | Updated Section 3                                                                               |   |  |  |  |  |

| •  | Updated document for additional clarity                                                         | 5 |  |  |  |  |

|    |                                                                                                 |   |  |  |  |  |

www.ti.com Revision History

| Cł | hanges from A Revision (February 2018) to C Revision                                            | Page |

|----|-------------------------------------------------------------------------------------------------|------|

| •  | Updated abstract                                                                                | 1    |

|    | Edited application report for clarity                                                           |      |

|    | Updated Section 1                                                                               |      |

| •  | Updated Section 2                                                                               | 2    |

|    | Deleted BQ2589X family register addresses from body of text and added BQ2588X family in Table 1 |      |

|    | Updated Section 3                                                                               |      |

| •  | Updated document for additional clarity                                                         | 5    |

|    | ·                                                                                               |      |

Revision History www.ti.com

| Cł | nanges from Original (August 2016) to A Revision                                 | Page |

|----|----------------------------------------------------------------------------------|------|

| •  | Changed 3.25 A to 3 A in the Case 4 Actual Input Current Limit column of Table 2 | 4    |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated