# Fundamentals of Precision ADC Noise Analysis

# Design tips and tricks to reduce noise with delta-sigma ADCs

#### About the author

Bryan Lizon is a product marketing engineer for the Precision Analog-to-Digital Converter (ADC) team at Texas Instruments (TI). In this role, Bryan has been responsible for the marketing functions for TI's factory automation and control, test and measurement, medical and automotive ADCs. He joined TI in 2014 as part of the Precision ADC team after receiving his Bachelor of Science degree in electrical engineering from the University of Arizona.

Bryan became interested in the topic of ADC noise soon after joining the ADC team, seeing that many disparate questions seemed like they could be traced back to challenges with noise, precision and resolution. Specifically, he found many customers had difficulty understanding the relationship between noise and gain, as well as how that related to data-sheet performance. To explore this relationship further and provide insight to engineers, Bryan wrote and illustrated a three-part **blog** post series framed as a whodunit mystery. From there, he took a more technical approach and expanded this topic to include multiple noise sources and how they interact with precision ADCs. Bryan turned this content into an internal presentation to educate TI's sales team, followed by an online series of 12 articles, which TI assembled into this e-book.

#### Other contributors include:

Christopher Hall, applications engineer, Precision ADCs Ryan Andrews, applications engineer, Precision ADCs Joachim Wuerker, systems manager, Precision ADCs

## Introduction from the author

When I first began working in the semiconductor industry, I had never heard of a delta-sigma analog-to-digital converter (ADC). My university training focused heavily on digital design, and the only ADCs we used were low-resolution successive-approximation-register (SAR) ADCs integrated into microcontrollers (MCUs). As a result, it was somewhat daunting to be assigned to the Precision ADC team, where digital knowledge is certainly useful, but analog design is king. As my training ramped up, I noticed that despite a variety of issues that engineers raised, many of their challenges arose from what seemed like a very obvious question: How do you get the best noise performance out of a 16-bit, 24-bit or even 32-bit ADC?

Now, I should note that this is a simple question with a complicated answer. And as is typical for most engineering questions, the answer is "It depends." "Depends on what?" you might ask—and exploring that question is the basis for this e-book. What affects a high-resolution ADC's noise performance? How does each component contribute noise to the system, and how do these noise sources interact with each other? Which noise source dominates, and how do you apply these principles to your specific application?

If you've ever been tasked with designing a signal chain that uses a delta-sigma ADC, you have likely had to ask yourself these questions. Regardless of your efforts to minimize power consumption, decrease board space or reduce cost, noise levels greater than the input signals render any design effectively useless. As a result, this e-book is designed to provide fundamental knowledge to help any analog designer understand signal-chain noise, its effect on analog-to-digital conversion, and how to minimize its impact and maintain high-precision measurements. I will examine common noise sources in a typical signal chain and complement this understanding with methods to mitigate noise and maintain high-precision measurements.

Before continuing, I'd like to mention that this e-book covers precision (noise), not accuracy. While the two terms are often used interchangeably, they refer to different—though related—aspects of signal-chain design. When designing high-performance data-acquisition systems, you must also consider errors due to inaccuracy, such as offset, gain error, integral nonlinearity and drift, in addition to minimizing noise.

# **Chapter 1: Introduction to ADC noise**

Chapter 1 encompasses three sections. In **Section 3.1**, I'll focus on analog-to-digital converter (ADC) noise fundamentals while answering questions and discussing topics such as:

- What is noise?

- Where does noise come from in a typical signal chain?

- Understanding inherent noise in ADCs.

- How is noise different in high-resolution vs. low-resolution ADCs?

In Section 3.2, I'll shift the focus to these topics:

- Measuring ADC noise.

- Noise specifications in ADC data sheets.

- Absolute vs. relative noise parameters.

In Section 3.3, I'll step through a complete design example, using a resistive bridge to help illustrate how the theories from Section 3.1 and Section 3.2 apply to a real-world application.

- Types of ADC noise •

- ADC noise measurement methods and parameters

- Defining system noise performance •

## **Types of ADC noise**

Noise is any undesired signal (typically random) that adds to the desired signal, causing it to deviate from its original value. Noise is inherent in all electrical systems, so there is no such thing as a "noise-free" circuit.

**Figure 1** depicts how you might experience noise in the real world: an image with the noise filtered out and that same image with no filtering. Note the crisp detail in **Figure 1**a, while **Figure 1**b is almost completely obscured. In the analog-to-digital conversion process, the result would be information loss between the analog input and the digital output—much like how the two images in **Figure 1** bear virtually no resemblance to each other.

In electronic circuits, noise comes in many forms, including:

- **Broadband (thermal, Johnson) noise**, which is temperature-dependent noise caused by the physical movement of charge inside electrical conductors.

- 1/f (pink, flicker) noise, which is low-frequency noise that has a power density inversely proportional to frequency.

- **Popcorn (burst) noise**, which is low frequency in nature and caused by device defects, making it random and mathematically unpredictable.

(a) High-resolution image example

(b) Noisy image example

Figure 1. A noise-free image (a) and the same image with noise (b)

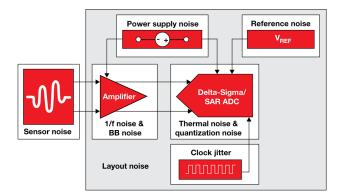

These forms of noise may enter the signal chain through multiple sources, including:

- **ADCs**, which contribute a combination of thermal noise and quantization noise.

- Internal or external amplifiers, which can add broadband and 1/f noise that the ADC then samples, allowing it to affect the output code result.

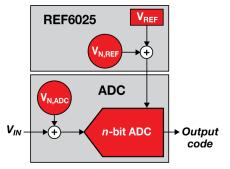

- Internal or external voltage references, which also contribute broadband and 1/f noise that appears in the ADC's output code.

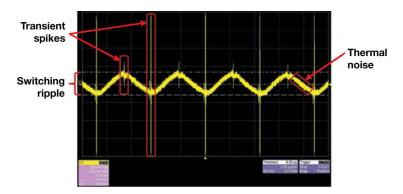

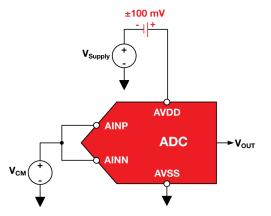

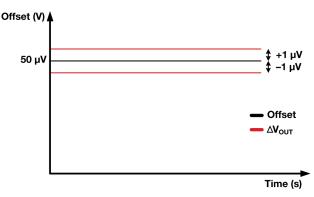

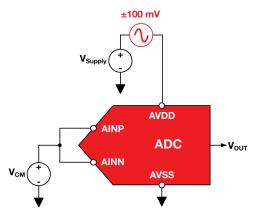

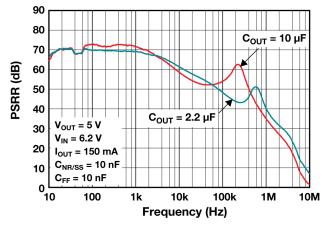

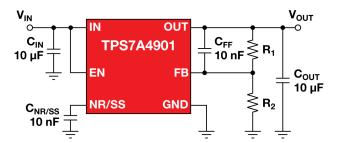

- **Nonideal power supplies**, which may add noise into the signal you're trying to measure with several means of coupling.

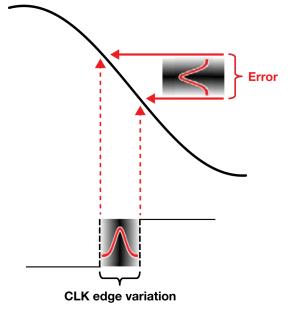

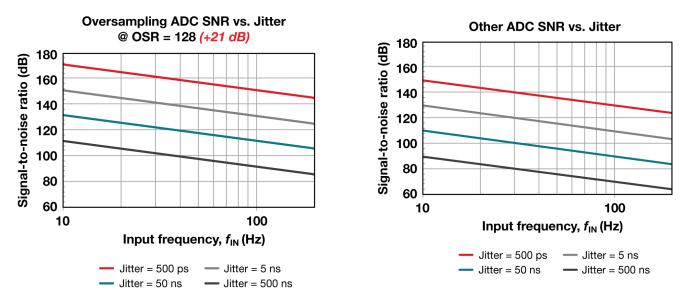

- **Internal or external clocks,** which contribute jitter that translates into nonuniform sampling. This appears as an additional noise source for sinusoidal input signals and is generally more critical for higher-speed ADCs.

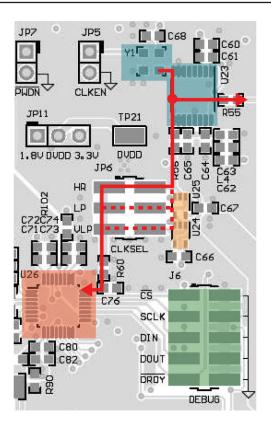

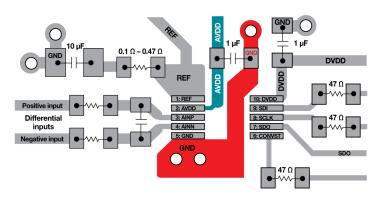

- **Poor printed circuit board (PCB) layouts**, which can couple noise from other parts of the system or environment into sensitive analog circuitry.

- **Sensors**, which can be one of the noisiest components in high-resolution systems.

Figure 2 depicts these noise sources in a typical signal chain.

Figure 2. Common noise sources in a typical signal chain

In the three sections that make up Chapter 1, I'll focus on inherent ADC noise only. For a more comprehensive understanding of signal-chain noise, Chapters 3–6 discuss sources of noise in the remaining circuit components.

## Inherent noise in ADCs

You can categorize total ADC noise into two main sources: quantization noise and thermal noise. These two noise sources are uncorrelated, which enables the root-sum-square method to determine the total ADC noise, N<sub>ADC,Total</sub>, as shown in **Equation 1**:

$$N_{ADC, Total} = \sqrt{N_{ADC, Thermal}^2 + N_{ADC, Quantization}^2}$$

Each ADC noise source has particular properties that are important when understanding how to mitigate inherent ADC noise.

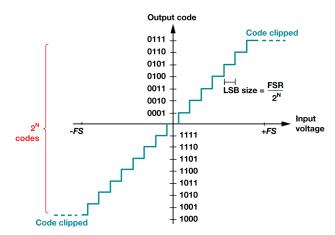

**Figure 3** depicts the plot of an ADC's ideal transfer function (unaffected by offset or gain error). The transfer function extends from the minimum input voltage to the maximum input voltage horizontally and is divided into a number of steps based off the total number of ADC codes along the vertical axis. This particular plot has 16 codes (or steps), representing a 4-bit ADC. (Note: An ADC using straight binary code would have a transfer function that only includes the first quadrant.)

(1)

Figure 3. An ADC's ideal transfer function

Quantization noise comes from the process of mapping an infinite number of analog voltages to a finite number of digital codes. As a result, any single digital output can correspond to several analog input voltages that may differ by as much as ½ least significant bit (LSB), which is defined in **Equation 2**:

$$LSB \ size \ (N) = \frac{FSR}{2^N}$$

(2)

where FSR represents the value of the full-scale range (FSR) in volts and N is the ADC's resolution.

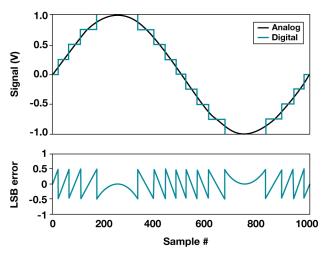

If you map this LSB error relative to a quantized AC signal, you'll get a plot like the one shown in **Figure 4**. Note the dissimilarity between the quantized, stair-step-shaped digital output and the smooth, sinusoidal analog input. Taking the difference between these two waveforms and plotting the result yields the sawtooth-shaped error shown at the bottom of **Figure 4**. This error varies between  $\pm \frac{1}{2}$  LSB and appears as noise in the result. 1.0

Figure 4. Analog input, digital output and LSB error waveforms.

Similarly, for DC signals, the error associated with quantization varies between  $\pm \frac{1}{2}$  LSB of the input signal. However, since DC signals have no frequency component, quantization "noise" actually appears as an offset error in the ADC output.

Finally, an obvious but important result of quantization noise is that the ADC cannot measure beyond its resolution, as it cannot distinguish between sub-LSB changes in the input.

Unlike quantization noise, which is a byproduct of the analog-to-digital (or digital-to-analog) conversion process, thermal noise is a phenomenon inherent in all electrical components as a result of the physical movement of charge inside electrical conductors. Therefore, you can measure thermal noise even without applying an input signal.

Unfortunately, you cannot affect your ADC's thermal noise because it is a function of the device design. Throughout the rest of this section, I'll refer to all ADC noise sources other than quantization noise as the ADC's thermal noise.

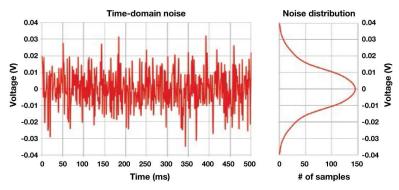

Figure 5 depicts thermal noise in the time domain, which typically has a Gaussian distribution.

Figure 5. Thermal noise in the time domain with Gaussian distribution.

Although you cannot affect the ADC's inherent thermal noise, you can potentially change the ADC's level of quantization noise due to its dependence on LSB size. Quantifying the significance of this change depends on whether you're using a "low-resolution" or "high-resolution" ADC, however. Let's quickly define these two terms so that you can better understand how to use LSB size and quantization noise to your advantage.

#### Low- vs. high-resolution ADCs

A low-resolution ADC is any device whose total noise is more dependent on quantization noise such that  $N_{ADC,Quantization}$ >>  $N_{ADC,Thermal}$ . Conversely, a high-resolution ADC is any device whose total noise is more dependent on thermal noise, such that  $N_{ADC,Quantization} << N_{ADC,Thermal}$ . The transition between low and high resolution typically occurs at the 16-bit level, with anything <16 bits considered low resolution and anything >16 bits considered high resolution. While not always true, I'll keep this general convention throughout the remainder of this e-book.

Why make the distinction at the 16-bit level? Let's look at two ADC data sheets to find out. **Table 1** a shows the actual noise tables for the TI **ADS114S08**, a 16-bit delta-sigma ADC, while **Table 1** b shows the noise tables for its 24-bit counterpart, the **ADS124S08**. Other than their resolutions, these ADCs are identical.

| Data Rate (SPS) | Gain        | Data Rate (SPS) | Gain       |  |

|-----------------|-------------|-----------------|------------|--|

| Dala hale (SPS) | 1           |                 | 1          |  |

| 2.5             | 76.3 (76.3) | 2.5             | 0.32 (1.8) |  |

| 5               | 76.3 (76.3) | 5               | 0.40 (2.4) |  |

| 10              | 76.3 (76.3) | 10              | 0.53 (3.0) |  |

| 16.6            | 76.3 (76.3) | 16.6            | 0.76 (7.2) |  |

| 20              | 76.3 (76.3) | 20              | 0.81 (4.8) |  |

| 50              | 76.3 (76.3) | 50              | 1.3 (7.2)  |  |

| 60              | 76.3 (76.3) | 60              | 1.4 (8.0)  |  |

| 100             | 76.3 (76.3) | 100             | 1.8 (9.2)  |  |

| 200             | 76.3 (76.3) | 200             | 2.4 (13)   |  |

| 400             | 76.3 (76.3) | 400             | 3.6 (19)   |  |

| 800             | 76.3 (76.3) | 800             | 5.0 (29)   |  |

| 1000            | 76.3 (76.3) | 1000            | 6.0 (32)   |  |

| 2000            | 76.3 (76.3) | 2000            | 7.8 (45)   |  |

| 4000            | 76.3 (95)   | 4000            | 15 (95)    |  |

| (a)             |             | (b)             |            |  |

In the noise table for the 16-bit ADS114S08, all of the input-referred noise voltages are the same regardless of data rate. Compare that to the 24-bit ADS124S08's input-referred noise values, which are all different and decrease/improve with decreasing data rates.

While this doesn't result in any definitive conclusions by itself, let's use Equation 3 and Equation 4 to calculate the LSB size for each ADC, assuming a 2.5-V reference voltage:

$$LSB_{ADS114S08} = \frac{2 \times V_{REF}}{2^N} = \frac{2 \times 2.5}{2^{16}} = 76.3 \,\mu V \tag{3}$$

$$LSB_{ADS124S08} = \frac{2 \times V_{REF}}{2^N} = \frac{2 \times 2.5}{2^{24}} = 0.298 \,\mu V \tag{4}$$

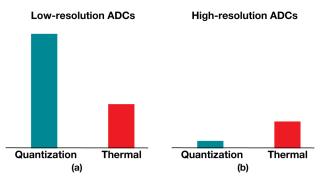

Combining these observations, you can see that the low-resolution (16-bit) ADC's noise performance as reported in its data sheet is equivalent to its LSB size (maximum quantization noise). On the other hand, the noise reported in the high-resolution (24-bit) ADC's data sheet is clearly much larger than its LSB size (quantization noise). In this case, the high-resolution ADC's quantization noise is so low that it's effectively hidden by the thermal noise. Figure 6 represents this comparison qualitatively.

Figure 6. Qualitative representation of quantization noise and thermal noise in low- (a) and high-resolution (b) ADCs.

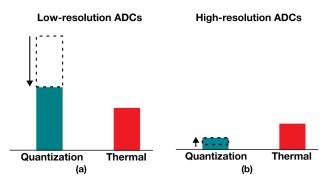

How can you use this result to your advantage? For low-resolution ADCs where quantization noise dominates, you can use a smaller reference voltage to reduce the LSB size, which reduces the quantization noise amplitude. This has the effect of lowering the ADC's total noise, represented by **Figure 7**a.

For high-resolution ADCs where thermal noise dominates, use a larger reference voltage to increase the input range (dynamic range) of the ADC, while ensuring that the quantization noise level remains below the thermal noise. Assuming no other system changes, this increased reference voltage enables a better signal-to-noise ratio, which you can see in **Figure 7**b.

Figure 7. Adjusting quantization noise in low- (a) and high-resolution (b) ADCs to improve performance.

Now that you understand the components of ADC noise and how they vary between high- and low-resolution ADCs, let's build on that knowledge.

#### Key takeaways

Here is a summary of important points to better understand types of ADC noise:

- 1. Noise is inherent in all electrical systems.

- 2. Noise is introduced via all signal chain components.

- 3. There are two main types of ADC noise:

- Quantization noise, which scales with the reference voltage.

- Thermal noise, which is a fixed value for a given ADC.

- 4. One type of noise generally dominates depending on the ADC's resolution:

- High-resolution ADC characteristics:

- Thermal noise-dominated.

- The resolution is typically >1 LSB.

- Increase the reference voltage to increase the dynamic range.

- Low-resolution ADC characteristics:

- Quantization noise-dominated.

- The resolution is typically limited by LSB size.

- Decrease the reference voltage to decrease the quantization noise and increase the resolution.

## ADC noise measurement methods and parameters

Before I explain how ADC noise is measured, it's important to understand that when you look at ADC data-sheet specifications, the goal is to characterize the ADC, not the system. As a result, the way that ADC manufacturers test ADC noise and the test system itself should demonstrate the capabilities of the ADC, not the limitations of the testing system. Therefore, using the ADC in a different system or under different conditions may lead to noise performance that varies from what the data-sheet reports.

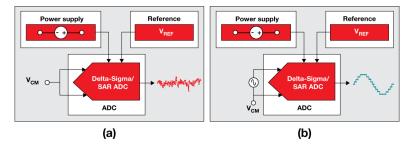

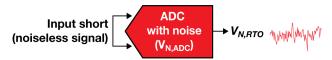

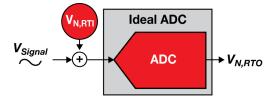

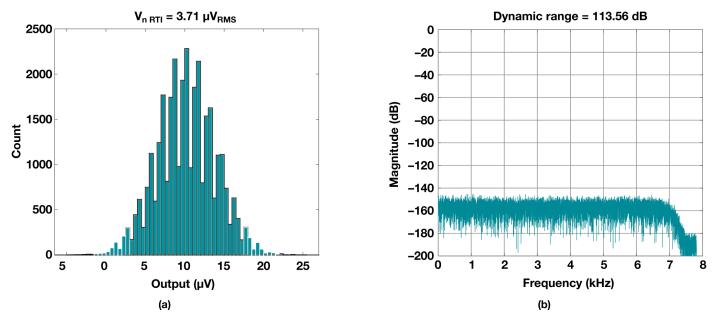

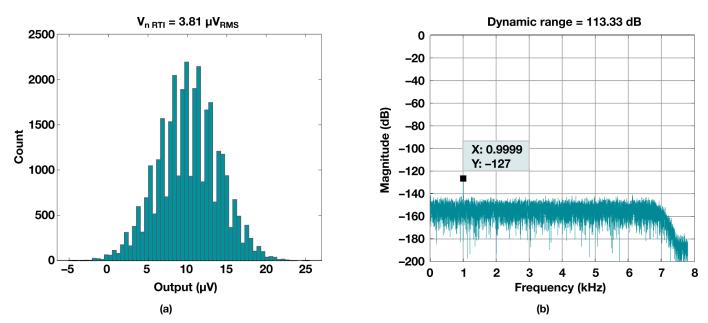

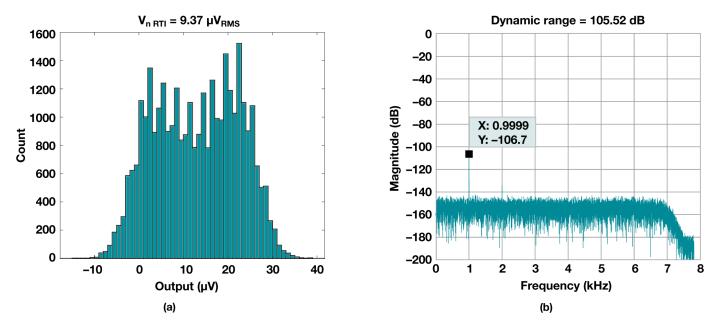

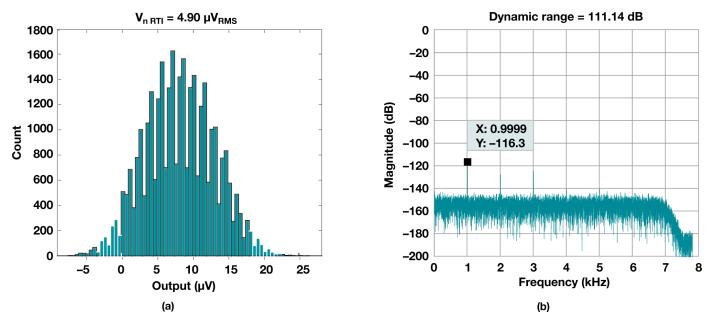

There are two methods ADC manufacturers use to measure ADC noise. The first method shorts the ADC's inputs together to measure slight variations in output code as a result of thermal noise. The second method involves inputting a sine wave with a specific amplitude and frequency (such as 1 V<sub>PP</sub> at 1 kHz) and reporting how the ADC quantizes the sine wave. **Figure 8** demonstrates these types of noise measurements.

#### Figure 8. Input-short test setup (a) and sine-wave-input test setup (b).

Typically, ADC manufacturers choose an individual ADC's noise measurement method based on its target end application(s). For example, delta-sigma ADCs that measure slow-moving signals such as temperature or weight use the input-short test, which precisely measures performance at DC. Delta-sigma ADCs used in high-speed data-acquisition systems generally rely on the sine-wave-input method, where AC performance is critical. For many ADCs, the data sheet specifies both types of measurements.

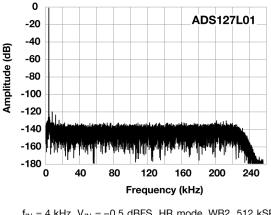

For example, the 24-bit **ADS127L01** from TI has a high maximum sampling rate of 512 kSPS and a low pass-band ripple wideband filter, both of which enable high-resolution AC signal sampling for test and measurement equipment. However, these applications often require accurate measurement of the signal's DC component as well. As a result, TI characterizes not only the ADC's performance with a range of AC input signals at multiple sample rates, but also the ADS127L01's DC performance using the input-short test.

#### Noise specifications in ADC data sheets

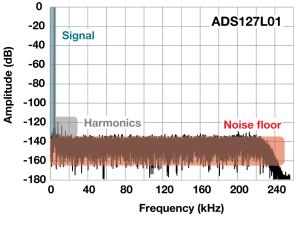

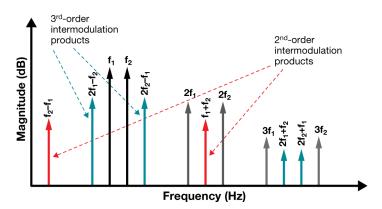

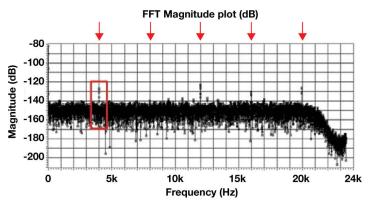

If you look at the ADS127L01's data sheet—or almost any ADC data sheet, for that matter—you'll see noise performance reported in two forms: graphically and numerically. **Figure 9** shows a fast Fourier transform (FFT) of the ADS127L01's noise performance using an input sine wave with an amplitude of –0.5 dbFS and a 4-kHz frequency. This plot makes it possible to calculate and report important AC parameters such as the signal-to-noise ratio (SNR), total harmonic distortion (THD), signal-to-noise ratio and distortion (SINAD) and effective number of bits (ENOB).

$f_{\text{IN}}$  = 4 kHz,  $V_{\text{IN}}$  = –0.5 dBFS, HR mode, WB2, 512 kSPS, 32768 samples

#### Figure 9. Example ADS127L01 FFT with a 4-kHz, -0.5-dBFS input signal.

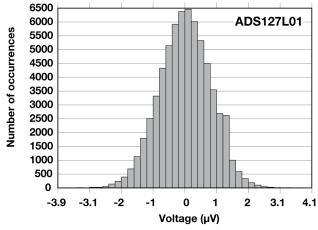

For DC performance, a noise histogram shows the distribution of output codes for a specific gain setting, filter type and sample rate. This plot makes it possible to calculate and report important DC noise performance parameters such as input-referred noise, effective resolution and noise-free resolution. (Note: Many engineers use the terms "ENOB" and "effective resolution" synonymously to describe an ADC's DC performance. However, ENOB is purely a dynamic performance specification derived from SINAD and is not meant to convey DC performance. Throughout the rest of this e-book, I will use these terms accordingly. For more comprehensive parameter definitions and equations, see **Table 2** later in this section, Section 1.2.) **Figure 10** shows the noise histogram for the ADS127L01. 6500

Inputs shorted, HR mode, LL, 8 kSPS, 32768 samples

#### Figure 10. Example ADS127L01 noise histogram.

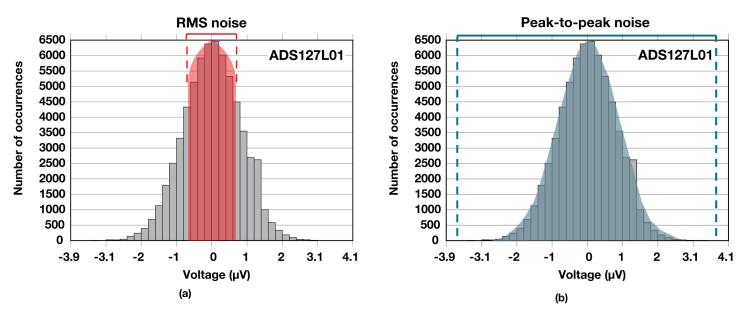

Like the FFT plot, the noise histogram provides important graphical information about DC noise performance. Since the noise histogram has a Gaussian distribution, the definition of average (root mean square [RMS]) noise performance is typically one standard deviation—the red-shaded region in **Figure 11**a.

Figure 11. ADS127L01 RMS (a) and peak-to-peak noise (b).

In **Figure 11**b, the teal-shaded region depicts the peak-to-peak ( $V_{N,PP}$ ) noise performance of the ADC. Peak-to-peak noise is given as 6 or 6.6 standard deviations due to the crest factor of Gaussian noise, which is the ratio of the peak value to the average value. Peak-to-peak noise defines the statistical probability that the measured noise will be within this range. If your input signal also falls in this range, there is a chance that it will be obscured by the noise floor, resulting in code flicker. Additional oversampling will help reduce peak-to-peak noise at the cost of a longer sampling time.

You'll also find the aforementioned AC and DC specifications numerically in the electrical characteristics section of most ADC data sheets. An exception to this rule involves ADCs with integrated amplifiers, where noise performance varies with gain as well as data rate. In such instances, there is generally a separate noise table for parameters such as input-referred noise (RMS or peak-to-peak), effective resolution, noise-free resolution, ENOB and SNR.

Table 2 summarizes AC and DC noise parameters, their definitions, the applicable noise test and equations.

| Noise parameter       | Definition                                                                                                                                                                                                | Noise test              | Equation (units)                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|

| Input-referred noise  | Resolution or internal noise of the ADC (plus programmable<br>gain amplifier [PGA] noise for integrated devices) specified<br>as a noise voltage source applied to the ADC's input pins<br>(before gain). | n/a                     | <i>Measured</i> (V <sub>RMS</sub> ,V <sub>PP</sub> )                                           |

| SNR                   | Ratio of the output signal amplitude to the output noise level, not including harmonics or DC.                                                                                                            | Input sine wave<br>(AC) | $10\log_{10}\left(\frac{V_{Signal(RMS)}}{V_{Noise(RMS)}}\right)$ (dBc)                         |

| THD                   | Indication of a circuit's linearity in terms of its effect on<br>the harmonic content of a signal, given as the ratio of the<br>summed harmonics to the RMS signal amplitude.                             | Input sine wave<br>(AC) | $10\log_{10}\left(\frac{\sum(V_{Harmonics})}{V_{Signal(RMS)}}\right)$ (dBc)                    |

| SINAD                 | Ratio of the RMS value of the output signal to the RMS value of all other spectral components, not including DC.                                                                                          | Input sine wave<br>(AC) | $10\log_{10}\left(\frac{V_{Signal}(RMS)}{\Sigma(V_{Harmonics}) + V_{Noise}(RMS)}\right)$ (dBC) |

| Effective resolution  | Dynamic range figure of merit using the ratio of full-scale<br>range (FSR) to RMS noise voltage to define the noise<br>performance of an ADC.                                                             | DC-input (DC)           | $\log_2\left(\frac{FSR}{V_{N,RMS}}\right)$ (bits)                                              |

| Noise-free resolution | Dynamic range figure of merit using the ratio of FSR to peak-to-peak noise voltage to define the maximum number of bits unaffected by peak-to-peak noise.                                                 | DC-input (DC)           | $\log_2\left(\frac{FSR}{V_{N,PP}}\right)$ (bits)                                               |

Table 2. Typical ADC noise parameters with definitions and equations.

Table 2. Typical ADC noise parameters with definitions and equations. (continued)

| Noise parameter | Definition                                                                                                                             | Noise test              | Equation (units)                                 |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|

|                 | Figure of merit representing the number of noise-free codes (or counts) that you can realize with noise.                               | DC-input (DC)           | 2 ( <i>Noise-free resolution</i> ) (counts)      |

|                 | Figure of merit relating the SINAD performance to that of an ideal ADC's resolution with a certain number of bits (given by the ENOB). | Input sine wave<br>(AC) | $\frac{\text{SINAD}(dBc) - 1.76dB}{6.02}$ (bits) |

#### Absolute vs. relative noise parameters

An important characteristic of all of the equations in **Table 2** is that they involve some ratio of values. These are "relative parameters." As the name implies, these parameters provide a noise performance metric relative to some absolute value, usually the input signal (decibels relative to carrier [dBc]) or the FSR (decibels relative to full scale [dBFS]).

Figure 12 shows an output spectrum of the ADS127L01 using an input signal at -0.5 dBFS, where full scale is 2.5 V.

$f_{\text{IN}}$  = 4 kHz,  $V_{\text{IN}}$  = –0.5 dBFS, HR mode, WB2, 512 kSPS, 32768 samples

Figure 12. ADS127L01 FFT, with the input voltage (V<sub>IN</sub>) referenced to full scale.

If you choose a system input signal that is not referenced to the same full-scale voltage, or if the input signal amplitude varies from the value defined in the data sheet, you should not necessarily expect to achieve data-sheet performance, even if all of your other input conditions are identical.

Similarly, for DC noise parameters, you can see from **Table 2** that effective resolution is relative to the ADC's inputreferred noise performance at the given operating conditions, as well as at the ADC's FSR. Since FSR depends on the ADC's reference voltage, using a reference voltage other than what's listed in the data sheet has an effect on your ADC's performance metrics.

For high-resolution ADCs, increasing the reference voltage increases the maximum input dynamic range, while inputreferred noise stays the same. That is because high-resolution ADC noise performance is largely independent of the reference voltage. For low-resolution ADCs, where noise is dominated by LSB size, increasing the reference voltage actually increases input-referred noise, while the maximum input dynamic range remains approximately the same. **Table 3** on the following page summarizes these effects.

Table 3. Effect of changing reference voltage on ADC noise parameters.

| Reference voltage | Parameter            | Low-resolution ADCs | High-resolution ADCs |  |

|-------------------|----------------------|---------------------|----------------------|--|

| Increases         | Dynamic range        | Stays the same      | Increases            |  |

| Increases         | Input-referred noise | Increases           | Stays the same       |  |

| Decreases         | Dynamic range        | Stays the same      | Decreases            |  |

| Decreases         | Input-referred noise | Decreases           | Stays the same       |  |

Therefore, to characterize an ADC's maximum dynamic range, most ADC manufacturers specify effective resolution and noise-free resolution, using the assumption that the FSR is maximized. Or, in other words, if your system does not use the maximum FSR (or whatever FSR the manufacturer used to characterize the ADC), you should not expect to achieve the effective or noise-free resolution values specified in the data sheet.

Let's illustrate this point by using a 1-V reference voltage with an ADC whose data-sheet noise is characterized with a reference voltage of 2.5 V. Continuing with the ADS127L01 as an example, **Table 4** shows that using a 2.5-V reference voltage and a 2-kSPS data rate in very low power mode results in 1.34 µVRMS of input-referred noise and an effective resolution of 21.83 bits.

| Mode                 | Data rate (SPS) | V <sub>RMS_noise</sub> (μV <sub>RMS</sub> ) | ENOB  |

|----------------------|-----------------|---------------------------------------------|-------|

|                      | 512,000         | 7.40                                        | 19.37 |

| High resolution (HR) | 128,000         | 5.12                                        | 19.90 |

| rightesolution (Fin) | 32,000          | 2.74                                        | 20.80 |

|                      | 8,000           | 1.41                                        | 21.76 |

|                      | 256,000         | 7.22                                        | 19.40 |

| Low power (LP)       | 64,000          | 4.97                                        | 19.94 |

|                      | 16,000          | 2.65                                        | 20.85 |

|                      | 4,000           | 1.37                                        | 21.80 |

|                      | 128,000         | 6.97                                        | 19.45 |

| Very-low power (VLP) | 32,000          | 4.80                                        | 19.99 |

|                      | 8,000           | 2.57                                        | 20.89 |

|                      | 2,000           | 1.34                                        | 21.83 |

Table 4. ADS127L01 noise performance: low-latency filter, AVDD = 3V, DVDD = 1.8 V and V<sub>REF</sub> = 2.5 V.

However, using a 1-V reference voltage reduces the FSR to 2 V. You can use this 2-V value to calculate the new expected effective resolution (dynamic range), given by **Equation 5**:

$$\log_2\left(\frac{FSR}{V_{Noise,RMS}}\right) = \log_2\left(\frac{2V}{1.34 \times 10^{-6}V}\right) = 20.51 \text{ bits}$$

(5)

Changing the reference voltage reduces the ADC's FSR, which in turn reduces its effective resolution (dynamic range) compared to the data-sheet value by more than 1.3 bits. **Equation 6** generalizes this loss of resolution:

$$\frac{resolution (dynamic}{range) loss} = \log_2(\% utilization) = \log_2\left(\frac{2V}{5V}\right) = -1.32 bits$$

(6)

where % utilization is simply the ratio of the actual FSR to the FSR at which the ADC's noise is characterized.

While this apparent resolution loss may seem like a drawback to using high-resolution delta-sigma ADCs, recall that while the FSR is decreasing, the input-referred noise is not. Therefore, I suggest performing ADC noise analysis using

an absolute noise parameter, or one that is measured directly. Using an absolute noise parameter eliminates the dependence on the input signal and reference voltage characteristic of relative noise parameters. Additionally, absolute parameters simplify the relationship between ADC noise and system noise.

For ADC noise analysis, I recommend using input-referred noise. I've bolded this phrase because it's not common practice to use input-referred noise to define ADC performance. In fact, a majority of engineers speak exclusively in terms of relative parameters such as effective and noise-free resolution, and are deeply concerned when they cannot maximize those values. After all, if you need to use a 24-bit ADC to achieve 16-bit effective resolution, it feels like you're paying for performance that the ADC cannot actually provide.

However, an effective resolution of 16 bits doesn't necessarily tell you anything about how much of the FSR you use. You may only need 16 bits of effective resolution, but if the minimum input signal is 50 nV, you will never be able to resolve that with a 16-bit ADC. Therefore, the true benefit of a high-resolution delta-sigma ADC is the low levels of input-referred noise it offers. It does not mean that effective resolution is unimportant—just that it is not the best way to parameterize a system.

Ultimately, if the ADC cannot resolve both the minimum and maximum input signals, maximizing SNR or effective resolution is irrelevant. And unlike effective resolution, you can typically derive the ADC's required input-referred noise directly and easily from the system specifications. This characteristic makes input-referred noise analysis more flexible to system changes. Additionally, it enables easy comparison between different ADCs in order to choose a specific ADC for any application.

#### Key takeaways

Here is a summary of important points to better understand ADC noise measurement methods and parameters:

- 1. Different measurements quantify different types of noise:

- To measure AC noise performance, use the AC-signal applied test.

- To measure DC noise performance, use the input-short test.

- ADC end applications typically determine the noise measurement type.

- 2. Noise is introduced via all signal-chain components.

- In general, assume that the input signal is equal to the FSR.

- 3. There are two types of noise parameters:

- Relative-calculated using a ratio of measured values.

- Absolute-measured directly.

- 4. Input-referred noise is the absolute measure of an ADC's resolution (the smallest measurable signal). Noise-free bits and effective resolution are relative parameters that describe the dynamic range of the ADC.

## Defining system noise performance

In Section 3.1 and Section 3.2, I explored ADC noise performance in detail, from its characteristics and sources to how it's measured and specified. Now, I'll apply the theoretical understanding from Section 3.1 and Section 3.2 to a real-world design example. Ultimately, the goal is to give you the knowledge necessary to answer the question, "What noise performance do I really need?," allowing you to easily and confidently choose an ADC for your next application.

#### System specifications

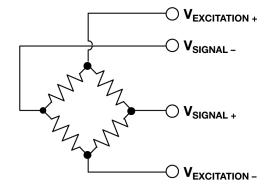

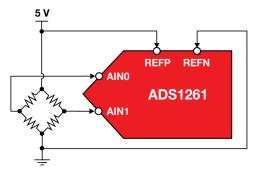

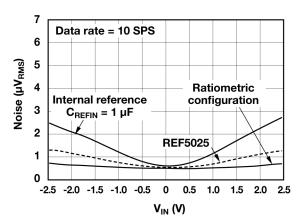

I'll begin the example by defining system specifications for the application, converting these specifications into a target noise-performance parameter, and using that information to compare potential ADCs. As an example, let's analyze a weigh-scale application that uses a four-wire resistive bridge similar to that shown in **Figure 13**.

#### Figure 13. Typical four-wire resistive bridge.

For the system specifications, assume a bridge with a sensitivity of 2 mV/V and an excitation voltage of 2.5 V that you want to sample at 5 samples per second (SPS). This provides a maximum output voltage of 5 mV that corresponds to a weight range of 1 kg. Let's also assume that you want to be able to resolve a minimum applied weight of 50 mg. **Table 5** summarizes these parameters.

| Parameter                    | System specification |

|------------------------------|----------------------|

| Bridge sensitivity           | 2 mV/V               |

| Excitation/reference voltage | 2.5 V                |

| Output data date             | 5 SPS                |

| Weight range                 | 1 kg                 |

| Weight resolution            | 50 mg                |

Table 5 Example design system specifications

Now that you have the system specifications, let's convert them into common noise parameters to help you choose your ADC.

#### Defining a system noise parameter

In Section 3.2, I strongly recommended using input-referred noise to define system noise parameters and choose an ADC. But let's begin with the more common approach of using noise-free counts and noise-free resolution. Then you can compare this method to using input-referred noise directly. Equation 7 and Equation 8 calculate your initial noise parameters:

noise-free counts (NFC) =

$$\frac{\max signal}{\min signal} = \frac{1 kg}{50 mg} = 20,000 counts$$

(7)

noise-free resolution =  $\log_2(NFC) = \log_2(20,000) = 14.3 bits$  (8)

With a required noise-free resolution of 14.3 bits, you might quickly conclude that you only need a 16-bit ADC. However, as I explained in **Section 3.2**, the noise-free resolution that a high-resolution delta-sigma ADC can actually provide depends on the percent utilization of the ADC's full-scale range. In this example, the system uses a 2.5-V reference

voltage and the maximum input signal is the product of the excitation voltage (2.5 V) and bridge sensitivity (2 mV/V). **Equation 9** shows the expected resolution loss using **Equation 6** from **Section 3.2**:

$$\frac{resolution (dynamic}{range) loss} = \log_2 \left( \frac{2.5 V \times 2 \frac{mV}{V}}{2 \times 2.5 V} \right) = -9.96 \ bits \tag{9}$$

This is a dramatic result. Since you're only using 0.1% of the available full-scale range, you'll lose almost 10 bits of resolution. At this level, even a 24-bit ADC would not be sufficient to meet the system requirements. To remedy the issue, you'd need to increase the percent utilization by either changing the system specifications or amplifying the input signal. Assuming that you have little control over what the system requires, you're left with gaining up the input, an action that absolutely changes the noise performance of the signal chain.

Fortunately, you can continue your analysis without needing a detailed understanding of how amplifier noise affects system performance. Instead, you can use your existing knowledge to analyze the data-sheet noise tables of an ADC with an integrated PGA to determine if it meets the system requirements.

For example, **Table 6** shows the effective and noise-free resolution tables for the 24-bit **ADS124S08** up to 50 SPS, with the target data rate highlighted. Note that the ADS124S08 includes gains from 1 V/V up to 128 V/V.

Table 6. ADS124S08 effective resolution (noise-free resolution) – Sinc3 filter at AVDD = 3.3 V, AVSS = 0 V, PGA enabled, global chop disabled and an internal 2.5-V reference.

| Data rate | Gain        |             |             |             |             |             |             |             |  |

|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--|

| (SPS)     | 1 2         |             | 4           | 8           | 16          | 32          | 64          | 128         |  |

| 2.5       | 23.9 (21.4) | 23.9 (21.4) | 23.8 (21.4) | 23.6 (21.2) | 23.0 (20.5) | 22.6 (20.2) | 21.9 (19.1) | 21.0 (18.4) |  |

| 5         | 23.6 (21.0) | 23.5 (21.2) | 23.4 (21.0) | 23.2 (20.7) | 22.9 (20.0) | 22.2 (19.5) | 21.4 (18.9) | 20.5 (17.6) |  |

| 10        | 23.2 (20.7) | 23.0 (20.5) | 22.9 (20.4) | 22.8 (20.2) | 22.3 (19.6) | 21.7 (19.2) | 20.9 (18.4) | 20.1 (17.3) |  |

| 16.6      | 22.6 (20.2) | 22.7 (20.1) | 22.6 (20.0) | 22.4 (19.8) | 22.0 (19.4) | 21.3 (18.8) | 20.5 (17.9) | 19.7 (17.0) |  |

| 20        | 22.6 (20.0) | 22.5 (20.0) | 22.4 (19.8) | 22.3 (19.8) | 21.9 (19.3) | 21.2 (18.4) | 20.4 (17.7) | 19.6 (17.0) |  |

| 50        | 21.9 (19.4) | 21.9 (19.4) | 21.9 (19.3) | 21.7 (19.0) | 21.2 (18.6) | 20.5 (17.8) | 19.7 (17.2) | 18.9 (16.2) |  |

Table 7. Expected noise-free resolution (bits) using the ADS124S08.

| Data rate                       |       | Gain  |       |       |       |       |       |       |  |  |  |  |

|---------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Data rate                       | 1     | 2     | 4     | 8     | 16    | 32    | 64    | 128   |  |  |  |  |

| Data-sheet resolution<br>(bits) | 21.0  | 21.2  | 21.0  | 20.7  | 20.0  | 19.5  | 18.9  | 17.6  |  |  |  |  |

| Percent utilization             | 0.1%  | 0.2%  | 0.4%  | 0.8%  | 1.6%  | 3.2%  | 6.4%  | 12.8% |  |  |  |  |

| Resolution loss (bits)          | -9.97 | -8.97 | -7.97 | -6.97 | -5.97 | -4.97 | -3.97 | -2.97 |  |  |  |  |

| System resolution<br>(bits)     | 11.03 | 12.23 | 13.03 | 13.73 | 14.03 | 14.53 | 14.93 | 14.63 |  |  |  |  |

To determine if this ADC meets your requirements, you need to recalculate the expected resolution loss for each gain setting separately, as each results in a different percent utilization. You then need to add this to each corresponding noise-free resolution value reported in **Table 6** to see if it meets the system specifications. **Table 7** lists these different values as well as the calculated system noise-free resolution in bits using the ADS124S08 at a 5-SPS data rate.

Table 7 tells you that you can only achieve the required system noise-free resolution of 14.3 bits using a gain of 32, 64 or

128 V/V at 5 SPS.

Table 8 highlights these values in the context of the data-sheet noise tables.

One key takeaway from **Table 8** is that there is no simple way to correlate the values in the data sheet to the systemnoise parameter without multiple calculations. While this may not be relevant now after calculating the results, what if the system specifications suddenly change?

Suppose you decided to increase the excitation (reference) voltage from 2.5 V to 5 V. You're also going to increase the bridge sensitivity to 20 mV/V (which means that you cannot use the highest gain settings, since doing so will over-range the ADC). And you're exploring the option of sampling at 20 SPS instead of 5 SPS. How do these changes affect your ADC noise analysis?

To determine the answer, you would have to calculate a new resolution loss for each gain setting at the new data rate and reference voltage. Additionally, you would have to recreate the table in **Table 6** based off of a 5-V reference voltage, since this figure's calculations use a reference voltage of 2.5 V. Finally, you would have to recreate **Table 7** by subtracting the calculated resolution losses from the noise-free resolution table that was created using a 5-V reference voltage.

Admittedly, this is a lot of work, and is a direct result of noise-free resolution being a relative parameter. So let's now switch to using an absolute noise parameter, as I suggested in Section 1.2, and see how the analysis changes.

| Data rate |             |             |             | Gain        |             |             |             |             |

|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| (SPS)     | 1           | 2           | 4           | 8           | 16          | 32          | 64          | 128         |

| 2.5       | 23.9 (21.4) | 23.9 (21.4) | 23.8 (21.4) | 23.6 (21.2) | 23.0 (20.5) | 22.6 (20.2) | 21.9 (19.1) | 21.0 (18.4) |

| 5         | 23.6 (21.0) | 23.5 (21.2) | 23.4 (21.0) | 23.2 (20.7) | 22.9 (20.0) | 22.2 (19.5) | 21.4 (18.9) | 20.5 (17.6) |

| 10        | 23.2 (20.7) | 23.0 (20.5) | 22.9 (20.4) | 22.8 (20.2) | 22.3 (19.6) | 21.7 (19.2) | 20.9 (18.4) | 20.1 (17.3) |

| 16.6      | 22.6 (20.2) | 22.7 (20.1) | 22.6 (20.0) | 22.4 (19.8) | 22.0 (19.4) | 21.3 (18.8) | 20.5 (17.9) | 19.7 (17.0) |

| 20        | 22.6 (20.0) | 22.5 (20.0) | 22.4 (19.8) | 22.3 (19.8) | 21.9 (19.3) | 21.2 (18.4) | 20.4 (17.7) | 19.6 (17.0) |

| 50        | 21.9 (19.4) | 21.9 (19.4) | 21.9 (19.3) | 21.7 (19.0) | 21.2 (18.6) | 20.5 (17.8) | 19.7 (17.2) | 18.9 (16.2) |

Table 8. Gain settings that meet the system requirements using the ADS124S08 at a 5-SPS data rate.

Table 9. Gain and data-rate combinations providing  $\leq$ 250 nV<sub>PP</sub> using the ADS124S08. (Note: Table values are given as "noise  $\mu$ V<sub>RMS</sub> ( $\mu$ V<sub>PP</sub>)" using a 2.5-V reference voltage.)

| Data rate | Gain       |             |              |              |              |              |              |              |  |  |

|-----------|------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--|--|

| (SPS)     | 1          | 2           | 4            | 8            | 16           | 32           | 64           | 128          |  |  |

| 2.5       | 0.32 (1.8) | 0.16 (0.89) | 0.085 (0.45) | 0.049 (0.26) | 0.036 (0.20) | 0.025 (0.13) | 0.020 (0.14) | 0.019 (0.11) |  |  |

| 5         | 0.40 (2.4) | 0.21 (1.0)  | 0.11 (0.60)  | 0.066 (0.37) | 0.040 (0.30) | 0.033 (0.20) | 0.029 (0.16) | 0.027 (0.20) |  |  |

| 10        | 0.53 (3.0) | 0.29 (1.6)  | 0.16 (0.89)  | 0.088 (0.52) | 0.061 (0.39) | 0.046 (0.25) | 0.040 (0.23) | 0.036 (0.24) |  |  |

| 16.6      | 0.76 (4.2) | 0.36 (2.2)  | 0.20 (1.2)   | 0.11 (0.67)  | 0.077 (0.47) | 0.060 (0.35) | 0.052 (0.32) | 0.046 (0.30) |  |  |

| 20        | 0.81 (4.8) | 0.41 (2.4)  | 0.22 (1.4)   | 0.12 (0.71)  | 0.082 (0.48) | 0.064 (0.44) | 0.056 (0.37) | 0.048 (0.30) |  |  |

| 50        | 1.3 (7.2)  | 0.62 (3.7)  | 0.33 (1.9)   | 0.18 (1.2)   | 0.13 (0.76)  | 0.11 (0.69)  | 0.091 (0.53) | 0.080 (0.53) |  |  |

#### Using input-referred noise

Like noise-free resolution, you only need to know a few of your system specifications to determine the required inputreferred noise for your bridge. You need to know its maximum output signal, which is 5 mV. You also need to know the weight range to which this maximum signal corresponds, which is 1 kg. And finally, you need to know your weight resolution, which is 50 mg. With these few bits of information, you can use **Equation 10** to determine that your ADC needs to be able to resolve a peak-to-peak signal of 250 nV:

$$\frac{1\,kg}{50\,mg} = \frac{5\,mV}{?}, ? = 250\,nV_{PP}$$

(10)

One of the benefits of using input-referred noise is that you don't have to worry about calculating resolution loss. Instead, you can directly compare your calculated value against the input-referred noise table for your ADC to determine which combination of settings offers an equal or lower level of noise performance.

**Table 9** is an abridged version of the input-referred noise table for the ADS124S08. I've highlighted any combination of gain and data-rate settings that provides  $\leq$ 250 nV<sub>PP</sub> of input-referred noise.

If you compare the results in **Table 9** to your analysis using noise-free resolution in **Table 8**, you'll see that **Table 9** provides the entire range of ADS124S08 settings that meet the system requirements. **Table 8** only provides the values at the data rate selected and requires that you perform new calculations for different data rates, making this approach less adaptable to system specification changes.

#### Effects of system changes

Let's now assume that you've increased your weight range to 5 kg and your weight resolution to 500 mg, and kept your bridge's maximum output signal at 5 mV, as in **Equation 11**:

$$\frac{5\,kg}{500\,mg} = \frac{5\,mV}{?}, ? = 500\,nV_{PP} \tag{11}$$

With a quick calculation, you can determine that your system noise requirement has been relaxed to 500 nV<sub>PP</sub>, which makes more gain and data-rate combinations available to you. **Table 10** demonstrates that these relaxed system specifications allow you to sample faster (up to 20 SPS) or decrease your gain (down to 4 V/V) while still achieving the requisite noise performance.

| Data rate | Gain       |             |              |              |              |              |              |              |  |  |  |

|-----------|------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--|--|--|

| (SPS)     | 1          | 2           | 4            | 8            | 16           | 32           | 64           | 128          |  |  |  |

| 2.5       | 0.32 (1.8) | 0.16 (0.89) | 0.085 (0.45) | 0.049 (0.26) | 0.036 (0.20) | 0.025 (0.13) | 0.020 (0.14) | 0.019 (0.11) |  |  |  |

| 5         | 0.40 (2.4) | 0.21 (1.0)  | 0.11 (0.60)  | 0.066 (0.37) | 0.040 (0.30) | 0.033 (0.20) | 0.029 (0.16) | 0.027 (0.20) |  |  |  |

| 10        | 0.53 (3.0) | 0.29 (1.6)  | 0.16 (0.89)  | 0.088 (0.52) | 0.061 (0.39) | 0.046 (0.25) | 0.040 (0.23) | 0.036 (0.24) |  |  |  |

| 16.6      | 0.76 (4.2) | 0.36 (2.2)  | 0.20 (1.2)   | 0.11 (0.67)  | 0.077 (0.47) | 0.060 (0.35) | 0.052 (0.32) | 0.046 (0.30) |  |  |  |

| 20        | 0.81 (4.8) | 0.41 (2.4)  | 0.22 (1.4)   | 0.12 (0.71)  | 0.082 (0.48) | 0.064 (0.44) | 0.056 (0.37) | 0.048 (0.30) |  |  |  |

| 50        | 1.3 (7.2)  | 0.62 (3.7)  | 0.33 (1.9)   | 0.18 (1.2)   | 0.13 (0.76)  | 0.11 (0.69)  | 0.091 (0.53) | 0.080 (0.53) |  |  |  |

Table 10. Gain and data-rate combinations providing  $\leq$ 500 nV<sub>PP</sub> using the ADS124S08. (Note: Table values are given as "noise  $\mu$ V<sub>RMS</sub> ( $\mu$ V<sub>PP</sub>)" using a 2.5-V reference voltage.)

Table 11. Gain and data-rate combinations providing  $\leq$ 50 nV<sub>PP</sub> using the ADS1262. (Note: Table values are given as "noise  $\mu$ V<sub>RMS</sub> ( $\mu$ V<sub>PP</sub>)" using a 2.5-V reference voltage.)

| Data rate | Filter mode |               |               | Ga            | ain           |               |               |

|-----------|-------------|---------------|---------------|---------------|---------------|---------------|---------------|

| (SPS)     | Filler mode | 1             | 2             | 4             | 8             | 16            | 32            |

|           | FIR         | 0.145 (0.637) | 0.071 (0.279) | 0.038 (0.149) | 0.023 (0.089) | 0.014 (0.064) | 0.011 (0.051) |

|           | Sinc1       | 0.121 (0.510) | 0.058 (0.249) | 0.033 (0.143) | 0.018 (0.073) | 0.012 (0.054) | 0.008 (0.037) |

| 2.5       | Sinc2       | 0.101 (0.437) | 0.055 (0.225) | 0.025 (0.104) | 0.015 (0.064) | 0.010 (0.043) | 0.007 (0.031) |

|           | Sinc3       | 0.080 (0.307) | 0.046 (0.195) | 0.026 (0.116) | 0.013 (0.052) | 0.008 (0.034) | 0.006 (0.023) |

|           | Sinc4       | 0.080 (0.308) | 0.043 (0.180) | 0.020 (0.078) | 0.013 (0.049) | 0.008 (0.031) | 0.007 (0.027) |

|           | FIR         | 0.206 (1.007) | 0.098 (0.448) | 0.054 (0.252) | 0.028 (0.123) | 0.020 (0.098) | 0.015 (0.073) |

|           | Sinc1       | 0.161 (0.726) | 0.090 (0.432) | 0.047 (0.246) | 0.026 (0.120) | 0.017 (0.083) | 0.012 (0.057) |

| 5         | Sinc2       | 0.146 (0.661) | 0.069 (0.308) | 0.038 (0.195) | 0.021 (0.100) | 0.013 (0.061) | 0.011 (0.050) |

|           | Sinc3       | 0.128 (0.611) | 0.067 (0.325) | 0.033 (0.153) | 0.019 (0.095) | 0.012 (0.054) | 0.010 (0.046) |

|           | Sinc4       | 0.122 (0.587) | 0.063 (0.269) | 0.030 (0.144) | 0.017 (0.076) | 0.011 (0.048) | 0.008 (0.039) |

Table 11. Gain and data-rate combinations providing  $\leq$ 50 nV<sub>PP</sub> using the ADS1262. (Note: Table values are given as "noise  $\mu$ V<sub>RMS</sub> ( $\mu$ V<sub>PP</sub>)" using a 2.5-V reference voltage.) (continued)

| Data rate | Filter mode | Gain          |               |               |               |               |               |  |

|-----------|-------------|---------------|---------------|---------------|---------------|---------------|---------------|--|

| (SPS)     |             | 1             | 2             | 4             | 8             | 16            | 32            |  |

|           | FIR         | 0.284 (1.418) | 0.142 (0.753) | 0.077 (0.379) | 0.041 (0.197) | 0.027 (0.156) | 0.023 (0.118) |  |

|           | Sinc1       | 0.229 (1.220) | 0.123 (0.662) | 0.060 (0.322) | 0.035 (0.177) | 0.023 (0.118) | 0.018 (0.103) |  |

| 10        | Sinc2       | 0.193 (1.019) | 0.093 (0.488) | 0.048 (0.254) | 0.028 (0.149) | 0.019 (0.099) | 0.016 (0.079) |  |

|           | Sinc3       | 0.176 (0.896) | 0.088 (0.452) | 0.043 (0.217) | 0.028 (0.137) | 0.018 (0.091) | 0.014 (0.067) |  |

|           | Sinc4       | 0.164 (0.788) | 0.076 (0.389) | 0.040 (0.200) | 0.024 (0.119) | 0.016 (0.081) | 0.013 (0.065) |  |

What if your weigh scale requires more resolution instead? For example, you keep the 5-kg weight range requirement, but return to the 50-mg weight resolution from the first example. Keeping your maximum bridge output the same (5 mV), you now require 50 nV<sub>PP</sub> of input-referred noise, which is extremely low. Looking at **Table 9** or 10, it's clear that no combination of ADS124S08 gain and data rates provides this level of performance. But because you can easily perform this same analysis with any ADC, simply choose one with better noise performance.

Table 11 shows the noise table for the ADS1262 , a 32-bit ADC that is functionally similar to the ADS124S08 but offersbetter noise performance. The teal shading in Table 11 indicates the data-rate and noise combinations that provide  $\leq 50$  $nV_{PP}$  of input-referred noise, and confirm that the ADS1262 can meet your system's new resolution requirements.

For the sake of argument, let's compare the input-referred noise result to a relative parameter. **Table 12** highlights the ADS1262's noise-free resolution performance at the same data-rate and gain configurations shown in **Table 11**.

| Data rate | Filter mode | Gain        |             |             |                                                                     |             |             |  |

|-----------|-------------|-------------|-------------|-------------|---------------------------------------------------------------------|-------------|-------------|--|

| (SPS)     |             | 1 (Bypass)  | 2           | 4           | 8                                                                   | 16          | 32          |  |

|           | FIR         | 26.0 (23.9) | 25.9 (23.9) | 25.8 (23.8) | 25.5 (23.6)                                                         | 25.4 (23.0) | 24.6 (22.4) |  |

|           | Sinc1       | 26.3 (24.2) | 26.2 (24.1) | 26.0 (23.9) | 25.9 (23.8)                                                         | 25.6 (23.3) | 25.0 (22.8) |  |

| 2.5       | Sinc2       | 26.6 (24.4) | 26.3 (24.2) | 26.4 (24.3) | 26.1 (24.0)                                                         | 25.8 (23.6) | 25.2 (23.1) |  |

|           | Sinc3       | 26.9 (25.0) | 26.5 (24.4) | 26.3 (24.2) | 26.3 (24.3)                                                         | 26.1 (23.9) | 25.6 (23.5) |  |

|           | Sinc4       | 26.9 (25.0) | 26.6 (24.5) | 26.7 (24.7) | 8           25.5 (23.6)           25.9 (23.8)           26.1 (24.0) | 26.2 (24.1) | 25.2 (23.3) |  |

| 5         | FIR         | 25.5 (23.2) | 25.4 (23.2) | 25.3 (23.1) | 25.2 (23.1)                                                         | 24.8 (22.4) | 24.1 (21.9) |  |

|           | Sinc1       | 25.9 (23.7) | 25.5 (23.3) | 25.5 (23.1) | 25.4 (23.1)                                                         | 25.0 (22.7) | 24.4 (22.2) |  |

|           | Sinc2       | 26.0 (23.9) | 25.9 (23.8) | 25.8 (23.4) | 25.7 (23.4)                                                         | 25.4 (23.1) | 24.6 (22.4) |  |

|           | Sinc3       | 26.2 (24.0) | 26.0 (23.7) | 26.0 (23.8) | 25.8 (23.5)                                                         | 25.6 (23.3) | 24.7 (22.5) |  |

|           | Sinc4       | 26.3 (24.0) | 26.1 (24.0) | 26.1 (22.5) | 25.9 (23.8)                                                         | 25.7 (23.5) | 25.0 (22.8) |  |

|           | FIR         | 25.1 (22.7) | 24.9 (22.5) | 24.8 (22.5) | 24.7 (22.4)                                                         | 24.4 (21.8) | 23.5 (21.2) |  |

|           | Sinc1       | 25.4 (23.0) | 25.1 (22.7) | 25.1 (22.7) | 24.9 (22.6)                                                         | 24.6 (22.2) | 23.8 (21.4) |  |

| 10        | Sinc2       | 25.6 (23.2) | 25.5 (23.1) | 25.4 (23.0) | 25.2 (22.8)                                                         | 24.9 (22.4) | 24.1 (21.7) |  |

|           | Sinc3       | 25.8 (23.4) | 25.6 (23.2) | 25.6 (23.3) | 25.2 (22.9)                                                         | 25.0 (22.5) | 24.2 (22.0) |  |

|           | Sinc4       | 25.9 (23.6) | 25.8 (23.4) | 25.7 (23.4) | 25.5 (23.1)                                                         | 25.1 (22.7) | 24.4 (22.0) |  |

Table 12. Effective (noise-free) resolution correlating to  $\leq$ 50 nV<sub>PP</sub> using the ADS1262 and a 5-V reference voltage.

In Section 3.2, I pointed out that many engineers were unnecessarily concerned with maximizing their noise-free resolution (dynamic range). Let's examine this point by calculating your system's noise-free resolution from the largest highlighted value at the system-required 5-SPS data rate. In Table 12, this value is 23.5 bits and is available at a gain of 16 V/V using the Sinc4 filter.

Remember from **Table 12**'s caption that the table calculations use a 5-V reference voltage, not the 2.5-V reference voltage that the system specifies. To compensate for this difference, each of the resolution values given in **Table 11** must decrease by one bit. This means that you can only expect a maximum of 22.5 bits of noise-free resolution at the given conditions. You can now calculate the expected resolution loss for the ADS1262 at these settings.

Using the result from Equation 12, the system noise-free resolution is only 16.5 bits using a 32-bit ADC:

$$\frac{resolution (dynamic}{range) loss} = \log_2 \left( \frac{16\frac{V}{V} \times 2.5 V \times 2\frac{mV}{V}}{2 \times 2.5 V} \right) = -5.96 \text{ bits}$$

(12)

For many, this is a disheartening result that seems to confirm the fear that you are paying for performance the ADC cannot actually provide. However, if you look at the same settings from **Table 11**, you'll see that you're actually taking advantage of 48-nV<sub>PP</sub> noise at the given conditions. This is an incredibly small value that no 16-bit ADC and very few 24-bit ADCs can provide.

Ultimately, this is the point I'm trying to make. You need such a high-resolution ADC to achieve 16.5 bits of noise-free resolution (dynamic range) because the system requires extremely low noise performance. That is why it makes sense to define system performance and choose ADCs using input-referred noise.

In Section 4, I'll discuss effective noise bandwidth in detail and delve into topics including how to determine the amount of noise that passes into the system and methods to restrict noise bandwidth.

#### Key takeaways

Here is a summary of important points to better understand how to define system noise performance:

- 1. Use a common process:

- Convert sensor inputs (temperature, weight, current, resistance, etc.) to voltage.

- Define system resolution and range.

- Compare against ADC noise tables.

- 2. Input-referred noise is best to define system performance:

- Enables fair comparison between ADCs.

- Eliminates dependency on voltage reference.

- Provides a range of applicable-gain and data-rate settings.

- 3. Focus on resolving smallest and largest signals maximizing dynamic range is not always important.

# **Chapter 2: Effective noise bandwidth**

Understanding analog-to-digital converter (ADC) noise can be challenging—even for the most experienced analog designers. Delta-sigma ADCs have a combination of quantization and thermal noise that varies depending on the ADC's resolution, reference voltage and output data rate (ODR). At a system level, noise analysis is further complicated by additional signal-chain components, many of which have dissimilar noise characteristics that make them challenging to compare.

If you want to be able to estimate the noise in your system, however, you must understand how much noise each component contributes, how one component's noise may affect another and which noise sources dominate. Although this may seem like a difficult task, you can use a signal chain's effective noise bandwidth (ENBW) to help simplify the process.

To that end, Chapter 2 is about noise in **delta-sigma ADCs**, and begins with developing an understanding of basic ENBW topics such as:

- What is ENBW?

- Why is ENBW important?

- What contributes to the system's ENBW?

I will then continue the ENBW discussion by stepping through a simple design example using a two-stage filter to explore these subjects:

- How to calculate ENBW.

- How system changes affect ENBW.

Effective noise bandwidth fundamentals •

2.2 Calculating effective noise bandwidth •

## Effective noise bandwidth fundamentals

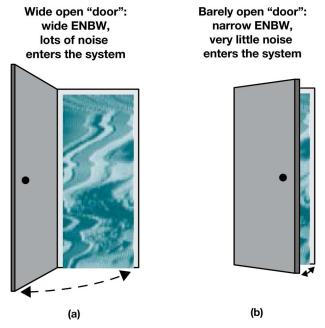

Since ENBW is an abstract concept, let's use the simple analogy of doors and windows on a cold night to understand it more easily. To reduce your energy costs and save money, you need to keep all of your doors and windows closed as much as possible in order to limit the amount of cold air entering your home. In this case, your home is the system, your doors and windows are the filter, the cold air is noise and ENBW is a measurement of how open (or closed) your openings are. The larger the gap (ENBW), the more cold air (noise) gets into your home (system) and vice versa, as shown in **Figure 14**.

Figure 14. A wide-open door equals more noise (a), while a barely open door equals less noise (b).

In general signal-processing terms, a filter's ENBW is the cutoff frequency,  $f_c$ , of an ideal brick-wall filter whose noise power is approximately equivalent to the noise power of the original filter, H(f). Relating this definition back to the door and window analogy, a system's ENBW is equivalent to combining the opening widths of each door and window— which may all be different—into one definable value that applies equally to them all. This simplification makes it much easier to understand how much "cold air" is getting in.

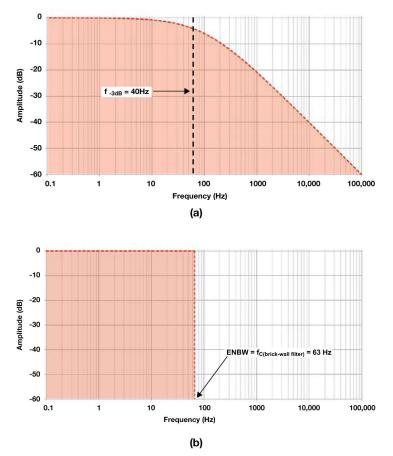

As an example, let's simplify a single-pole, low-pass resistor-capacitor (RC) filter (**Figure 15**a) into an ideal brick-wall filter (**Figure 15**b). To do so, calculate the noise power under the actual filter response using integration. This calculated value is the original filter's ENBW, which then becomes the cutoff frequency,  $f_c$ , of an analogous ideal brick-wall filter.

Figure 15. Single-pole RC filter response (a); ENBW plot for the RC filter (b).

In this case, you can calculate a single-pole, low-pass filter's ENBW using the direct-integration method, or you can use **Equation 13**, which relates the original RC filter's 3-dB point to its ENBW:

$ENBW_{1-pole RC filter} = 1.57 \times f_{-3 dB}$

(13)

For more information about how this formula was derived, see the TI Precision Labs training series on **operational amplifier (op amp) noise**.

With this simple example, ENBW is defined as the transformation from a real-world filter response to an ideal filter response. But let's discuss the motivation for using this technique and see how it can help simplify your noise analysis calculations.

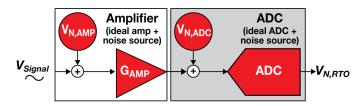

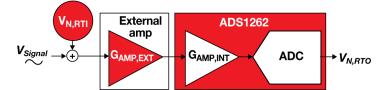

#### Why is ENBW important?

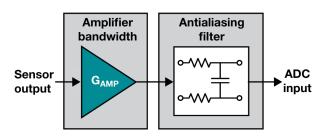

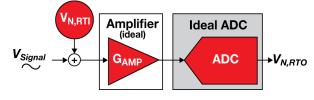

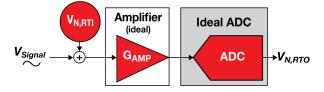

To understand why ENBW is important, let's assume that you want to use an ADC with no filtering to measure low-level resistive-bridge signals whose typical full-scale output can be as low as 10 mV. To accomplish this, you'll need to add an amplifier at the ADC's input to gain up your signals of interest above the ADC's noise floor, as well as widen the ADC's dynamic range. With no other filtering, the amplifier passes virtually all of its noise to the ADC. In this case, the noise is limited only by the amplifier's bandwidth, which could be thousands of kilohertz or more.

Fortunately, you'll also need to add an antialiasing filter after the amplifier. This filter performs two functions: first, it limits unwanted signals from folding back into the pass band; second, it reduces the signal chain's ENBW far more than the amplifier's bandwidth alone, given that **Equation 14** is generally true:

$BW_{Filter} \ll BW_{AMP}$

Figure 16 models the new ADC input stage.

Figure 16. ADC input stage with amplifier and antialiasing filter.

Given the condition in **Equation 15**, you know that the antialiasing filter limits the amplifier noise passing into the ADC but how much noise does it remove? Or, more importantly, how much noise still passes through to affect the ADC and the resulting measurement? In order to calculate this, you need to look at the amplifier's noise characteristics.

#### $BW_{Filter} \ll BW_{AMP}$

(15)

(14)

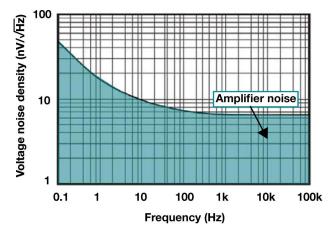

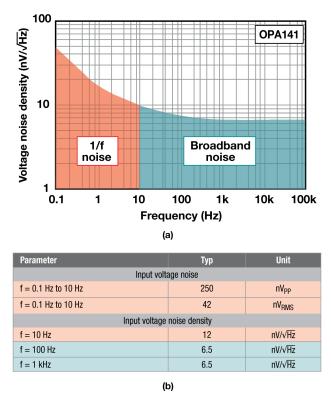

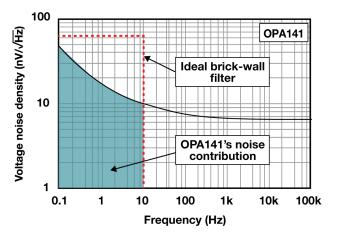

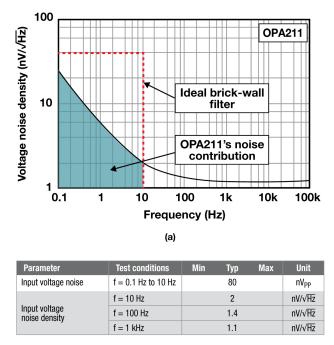

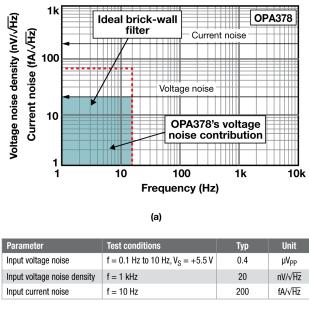

**Figure 17** shows an amplifier's voltage noise spectral density plot with a large 1/f (flicker) region. Taken by itself, this plot tells you very little about the amplifier's actual noise contribution (highlighted in teal). In fact, the nonconstant noise density—a common trait of nonchopper-stabilized amplifiers—makes it even more challenging to calculate how much noise passes to the ADC.

Figure 17. Generic amplifier noise density plot with a large 1/f region.

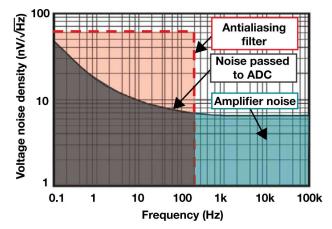

To find out how much noise passes to the ADC, you'll need to calculate the system's ENBW. Once you've determined the ideal brick-wall filter response, you can overlay it on the amplifier's noise spectral density curve, depicted by the red region in **Figure 18**.

#### Figure 18. Amplifier noise-density plot with overlaid ENBW.

The antialiasing filter in **Figure 18** is designed such that it provides a 200-Hz ENBW, effectively acting as a cutoff for the amplifier's noise. All that's left to do is calculate this noise, represented by the dark grey area in **Figure 18**. When broadband noise dominates, you can use **Equation 16** to calculate the root-mean-square (RMS) voltage noise:

#### $V_{Noise, Broadband} = V_{Noise spectral density} \times \sqrt{ENBW}$

If the device has a large 1/f noise component, similar to the amplifier shown in **Figure 17** and **Figure 18**, you can use direct integration or simplified formulas to calculate the device's noise contribution. For more information on each of these methods, please review the TI Precision Labs training module on **op amp noise**.

In this case, the calculated RMS voltage noise passed to the ADC is  $100nV_{RMS}$ .

#### What contributes to the system's ENBW?

Through this simple amplifier/antialiasing filter analysis, I inadvertently defined two sources that help determine a signal chain's ENBW. However, multiple filtering sources can exist in any design, and at least some filtering exists in every design. Even printed circuit boards (PCBs) that do not contain traditional filtering have trace impedances and parallel trace capacitances. These parasitics can create an unintentional RC filter, albeit one with a very large bandwidth and therefore little effect on the overall ENBW.

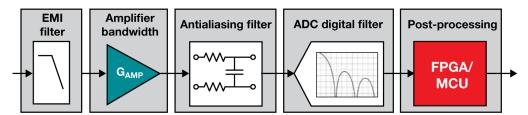

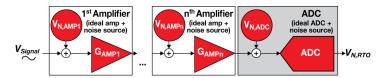

**Figure 19** highlights the most common sources of filtering in a typical data-acquisition (DAQ) system: external filters such as electromagnetic interference (EMI) filters, the amplifier's bandwidth, antialiasing filters, digital filters of delta-sigma ADCs and/or any post-processing filters created digitally in an MCU or field-programmable gate array. It's important to note that not all of these filtering sources appear in every signal chain. For example, many delta-sigma-based DAQ systems do not require post-processing filters due to the integrated filters inside these ADCs.

If your signal chain has multiple filter components, you must calculate each component's ENBW by combining all downstream filters in the signal chain. For example, to calculate the noise contribution of the amplifier in **Figure 19**, you would have to combine the amplifier's bandwidth with the antialiasing filter, the ADC's digital filter and any post-processing filters. However, you could ignore the EMI filter.

Fortunately, even if one circuit has multiple sources of filtering, some filter types generally have a greater effect on overall ENBW than others. As a result, you may only need to calculate that component's ENBW and ignore the other sources of filtering. For example, at lower-output data rates (ODRs), a delta-sigma ADC's digital filter typically provides

(16)

the narrowest bandwidth in the signal chain and therefore dominates the system's ENBW. Conversely, if you were to use a faster ODR with a very wide input-signal bandwidth, the antialiasing filter would generally limit the system's ENBW.

Now that you understand the fundamentals of ENBW, let's step through a simple example to help clarify how to apply ENBW to a real-world system.

Figure 19. Common sources of filtering in delta-sigma ADC DAQ systems.

#### Key takeaways

Here is a summary of important points to better understand ENBW fundamentals:

- 1. ENBW represents an ideal brick-wall filter's cutoff frequency for a given generic filter, H(f).

- 2. You must determine the ENBW for each noise source in the system.

- 3. To calculate each noise source's ENBW, combine all downstream filters in the system.

- 4. ENBW helps determine how much noise each component passes into the system.

- 5. ENBW is typically dominated by the filter with the smallest cutoff frequency, which is generally an antialiasing filter or digital filter, especially for precision delta-sigma ADCs.

## 2.2 Calculating effective noise bandwidth

Let's continue to explore ENBW as it relates to delta-sigma ADCs and system-level design, stepping through a simple example using a two-stage filter to understand:

- How to calculate ENBW.

- How system changes affect ENBW.

#### How to calculate ENBW

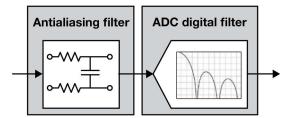

For this example, let's use a simple, two-stage DAQ system comprising an antialiasing filter followed by a **delta-sigma ADC** with an integrated sinc filter, shown in **Figure 20**. As I previously discussed, I'll focus on these two filter types because they typically have the greatest impact on the overall ENBW, but this analysis is generally applicable to any type or number of additional filters.

Figure 20. Simplified DAQ system block diagram.

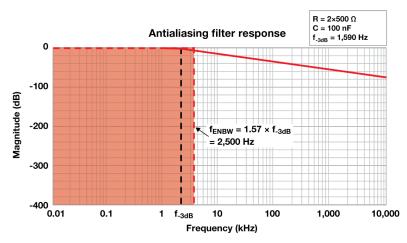

For the antialiasing filter, let's use a single-pole RC filter, since I already discussed how to calculate its ENBW in Section 2.1 (reiterated below in **Equation 17**). Moreover, a delta-sigma ADC typically only requires a simple RC filter to provide sufficient antialiasing. **Table 1** summarizes the chosen resistor and capacitor values for this example, though other valid combinations exist.

Table 13. Antialiasing filter component values.

| Antialiasing (RC) filter    |                       |  |  |  |

|-----------------------------|-----------------------|--|--|--|

| Resistors (W)               | 1,000 total (2 × 500) |  |  |  |

| Capacitor (nF)              | 100                   |  |  |  |

| -3-dB cutoff frequency (Hz) | 1,590                 |  |  |  |

With the passive component values selected, calculate the antialiasing filter's ENBW using Equation 17:

$ENBW_{1-pole RC filter} = 1.57 \times f_{-3 dB}$  $ENBW_{1-pole RC filter} = 1.57 \times 1,590 Hz = 2,500 Hz$

Finally, plot the antialiasing filter's response as shown in **Figure 21**, with the filter's ENBW represented by the red-shaded area.

Figure 21. Antialiasing filter response with ENBW highlighted.

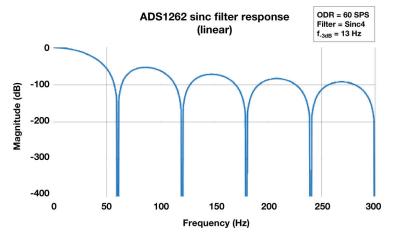

With a firm understanding of the antialiasing filter's frequency response, the next step is to determine the response of the ADC's sinc filter. For this example, let's choose the 32-bit, low-noise **ADS1262** from TI, although this analysis is generally applicable to any delta-sigma ADC. In this case, I'll use the ADS1262's Sinc4 filter at a data rate of 60 samples per second (SPS). **Figure 22** recreates a data-sheet plot for this filter's frequency response at these settings (derived from the **ADS1262 calculation tool**).

(17)

Figure 22. ADS1262 sinc filter response – linear frequency scale, f<sub>max</sub> = 300 Hz.

One subtle but important difference between these two filter response plots is that the sinc filter plot **Figure 22** uses a linear frequency axis, while the antialiasing filter plot **Figure 21** has a logarithmic frequency axis. This disparity results from the slow data rates of most delta-sigma ADCs, where showing multiple frequency decades is generally unnecessary. Unfortunately, this choice complicates the process of combining the filters into the same plot.

Additionally, recall that a sinc filter response repeats indefinitely—it does not simply "stop" at 300 Hz, as it might appear to in **Figure 22**.

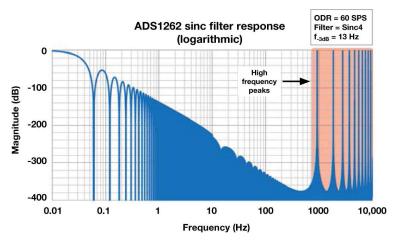

If you take both of these issues into consideration and plot the sinc filter response on a logarithmic axis over a much wider frequency range, the result in **Figure 23** is very different from the typical plot in most ADC data sheets.

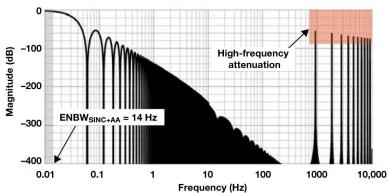

Figure 23. ADS1262 sinc filter response – logarithmic frequency scale, f<sub>max</sub> = 10 MHz.

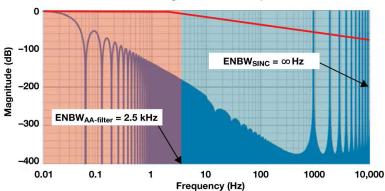

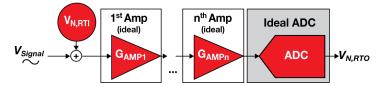

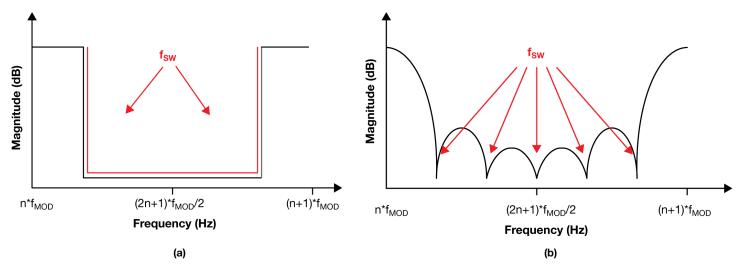

With a logarithmic axis plotted out to 10 MHz, you can now see the high-frequency peaks indicating the filter response repeating. Why is this important? As a result of this repetition, integrating under the sinc filter's frequency response curve yields an infinite ENBW (from a mathematical perspective, the sinc filter's integral diverges at infinity). **Figure 24** depicts a plot of both the antialiasing and sinc filter frequency responses as well as their respective ENBWs.

Antialiasing + sinc filter response

#### Figure 24. ENBWs of sinc and antialiasing filters.

How do you continue this analysis given the sinc filter's infinite ENBW? You simply need to set limits on the integration. Generally, some multiple (1 or 2) of the modulator clock frequency (f<sub>MOD</sub>) is acceptable, but in this case you can use the antialiasing filter as the limit.

Now that both filters are magnitude plots (in decibels [dB]) with the same x-axis scale, you can simply add them together to determine the overall system ENBW. This yields the filter response shown in **Figure 25**. Integrating the combined RC and digital filter response now results in an ENBW of 14 Hz, orders of magnitude smaller than either filter by itself.

Antialiasing + sinc filter response

Figure 25. System response of sinc and antialiasing filters.

The narrower ENBW results from the antialiasing filter's attenuation of the sinc filter noise power at higher frequencies, allowing less noise into the system. This also further explains why you don't necessarily need to account for the infinite frequency response of the sinc filter. The antialiasing filter already removes much of the noise power associated with the high-frequency peaks occurring at multiples of  $f_{MOD}$  that would **otherwise fold back into the passband**. Many analog designers assume that the antialiasing filter's intended purpose is to remove low-frequency noise, which is generally the responsibility of the **delta-sigma ADC's digital filter**.

If you followed this assumption and attempted to **design an antialiasing filter** with a very low cutoff frequency, you would generally need to use large resistor and capacitor values. However, large passive component values lead to longer signal settling times, which you generally want to avoid. Even if you could accept an additional settling time, ADC input leakage currents can cause significant offset voltages across large filter resistors, leading to system-level inaccuracy.

Thus, it is actually to the system's benefit that you only need to design antialiasing filters for high-frequency noise, as smaller passive components can help avoid the aforementioned issues.

#### How system changes affect ENBW

Suppose you now want to change the ADC's sample rate or the antialiasing filter's cutoff frequency. How does this affect the system ENBW? Intuitively, it would make sense that the filter with the smaller cutoff would dominate the ENBW calculation—as I have already shown—and this is a generally correct assumption. To illustrate this point, **Table 14** lists all available digital filter ODRs of the ADS1262, as well as the corresponding system ENBW for a range of antialiasing cutoff frequencies. **Table 14** also provides the ADC's 3-dB point, which effectively acts as its cutoff frequency.

System ENBW (Hz) ADS1262 data rate ADS1262 Sinc4 filter 3 Antialiasing filter (fc = Antialiasing filter (f<sub>C</sub> = Antialiasing filter (f<sub>C</sub> = Antialiasing filter (f<sub>C</sub> = (SPS) dB (Hz) 2.500 Hz) 25,000 Hz) 25 Hz) 250 Hz) 2.5 0.59 0.58 0.59 0.59 0.59 5 1.15 1.19 1.19 1.19 1.19 10 2.28 2.37 2.39 2.39 2.39 16.7 3.92 3.98 3.99 4.31 3.80 4.79 20 4.68 4.78 4.78 4.63 50 10.72 11.96 11.97 12.09 11 60 13 12.40 14.34 14.37 14.40 100 17.69 23.82 23.96 24.10 22 400 90 30.87 88.83 95.77 96.16 1.200 272 36.10 196.79 285.11 288.13 2,400 543 37.62 267.42 556.39 574.60 4,800 319.89 1,137.07 1,076 38.42 1,026.41 7.200 1,580 38.69 340.86 1.392.37 1.676.52 14,400 2,930 38.95 363.18 2,048.71 3,077.72 2.353.61 19,200 3.900 39.03 370.23 4,076.05

Table 14. Effect of ADC data rate and antialiasing filter cutoff frequency on a system's ENBW.

(1) Derived from the ADS1262 calculator tool.

The colored sections in Table 13 represent the following situations:

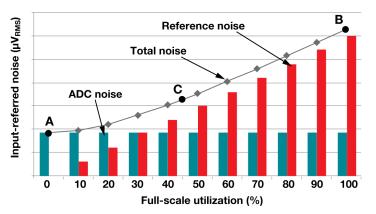

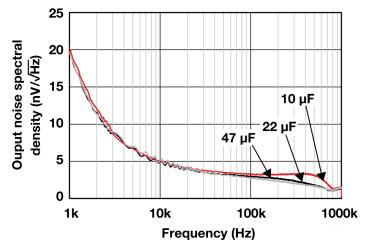

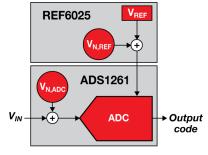

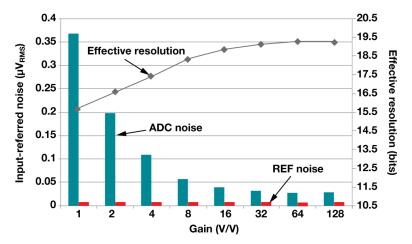

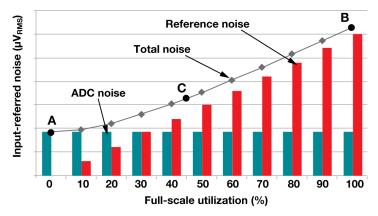

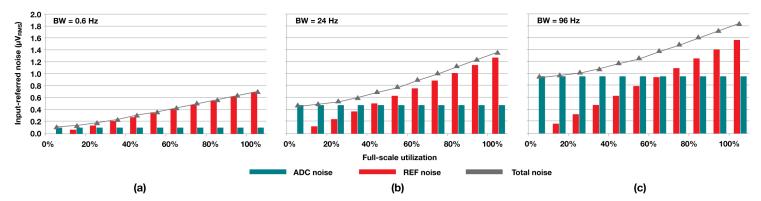

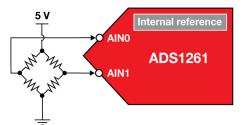

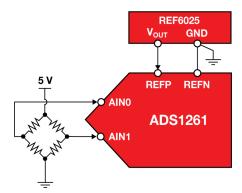

| $### = where f_{3 dB (ADC)} \le f_{C,(AA filter)}$ | ### = where $f_{3 \text{ dB (ADC)}} \ge 10 \times f_{C,(AA \text{ filter})}$ | ### = where $f_{3 \text{ dB (ADC)}} < 10 \times f_{C,(AA \text{ filter})} \text{ AND } f_{3 \text{ dB (ADC)}} > f_{C,(AA \text{ filter})}$ |