# TMS320DM646x DMSoC Asynchronous External Memory Interface (EMIF)

# **User's Guide**

Literature Number: SPRUEQ7C February 2010

| Pref | ace     |                                                        | 6          |

|------|---------|--------------------------------------------------------|------------|

| 1    | Introd  | uction                                                 | 8          |

|      | 1.1     | Purpose of the Peripheral                              | 8          |

|      | 1.2     | Features                                               | 8          |

|      | 1.3     | Functional Block Diagram                               | 9          |

| 2    | Archit  | ecture                                                 | 9          |

|      | 2.1     | Clock Control                                          | 9          |

|      | 2.2     | EMIF Requests                                          | 9          |

|      | 2.3     | Signal Descriptions                                    | 10         |

|      | 2.4     | Pin Multiplexing                                       | 10         |

|      | 2.5     | Asynchronous Controller and Interface                  | 10         |

| 3    | Use C   | ases                                                   | <b>30</b>  |

|      | 3.1     | Interfacing to Asynchronous SRAM (ASRAM)               | 30         |

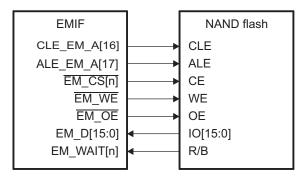

|      | 3.2     | Interfacing to NAND Flash                              | 39         |

| 4    | Regist  | ers                                                    | 48         |

|      | 4.1     | Revision Code and Status Register (RCSR)               | 49         |

|      | 4.2     | Asynchronous Wait Cycle Configuration Register (AWCCR) | <b>5</b> 0 |

|      | 4.3     | Asynchronous n Configuration Registers (A1CR-A4CR)     | <b>52</b>  |

|      | 4.4     | EMIF Interrupt Raw Register (EIRR)                     | 53         |

|      | 4.5     | EMIF Interrupt Mask Register (EIMR)                    | 54         |

|      | 4.6     | EMIF Interrupt Mask Set Register (EIMSR)               | 56         |

|      | 4.7     | EMIF Interrupt Mask Clear Register (EIMCR)             | 58         |

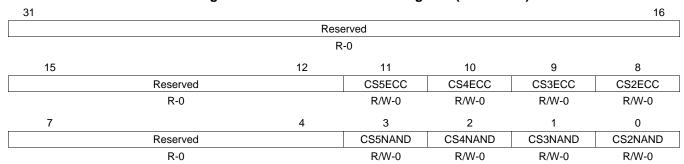

|      | 4.8     | NAND Flash Control Register (NANDFCR)                  | <b>60</b>  |

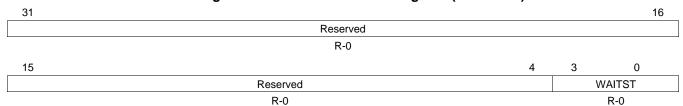

|      | 4.9     | NAND Flash Status Register (NANDFSR)                   | 61         |

|      | 4.10    | NAND Flash n ECC Registers (NANDF1ECC-NANDF4ECC)       | 61         |

| App  | endix A | Revision History                                       | <b>63</b>  |

# **List of Figures**

| 1  | EMIF Functional Block Diagram                                        | 9  |

|----|----------------------------------------------------------------------|----|

| 2  | EMIF Asynchronous Interface                                          | 11 |

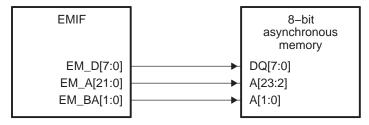

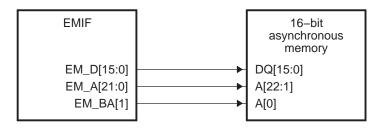

| 3  | EMIF to 8-bit and 16-bit Memory Interfaces                           | 11 |

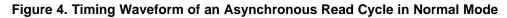

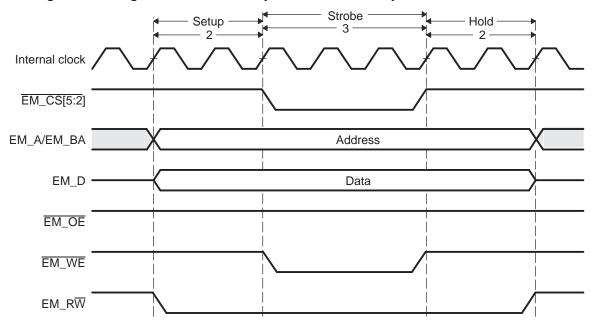

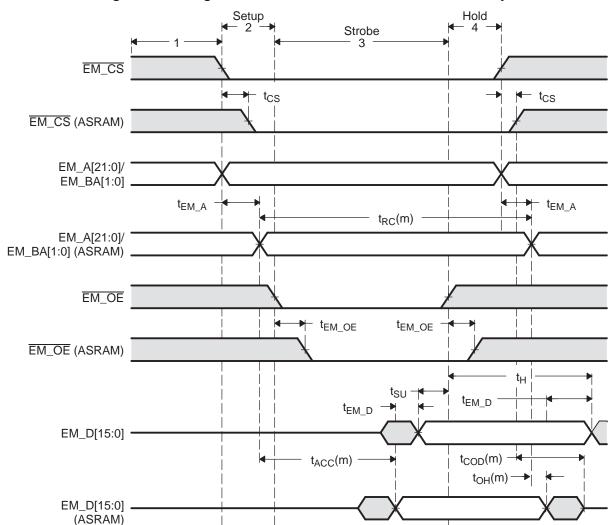

| 4  | Timing Waveform of an Asynchronous Read Cycle in Normal Mode         | 15 |

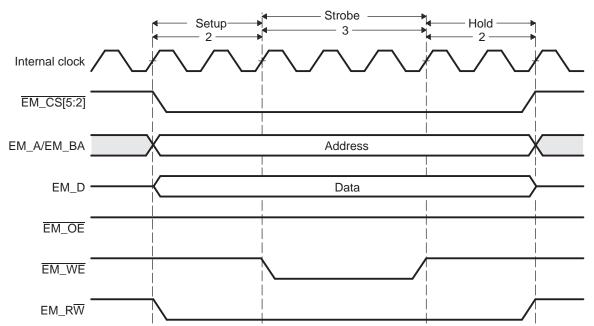

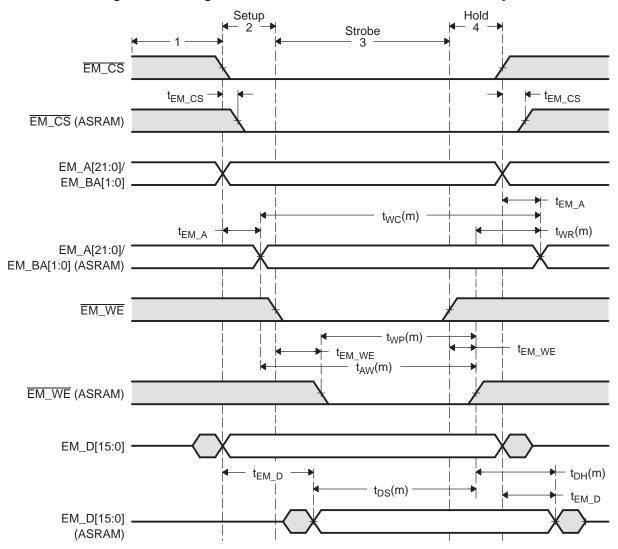

| 5  | Timing Waveform of an Asynchronous Write Cycle in Normal Mode        | 17 |

| 6  | Timing Waveform of an Asynchronous Read Cycle in Select Strobe Mode  | 19 |

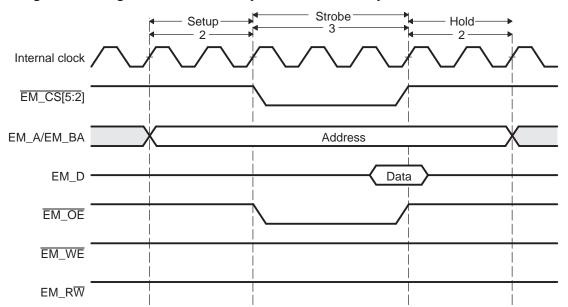

| 7  | Timing Waveform of an Asynchronous Write Cycle in Select Strobe Mode | 21 |

| 8  | EMIF to NAND Flash Interface                                         | 23 |

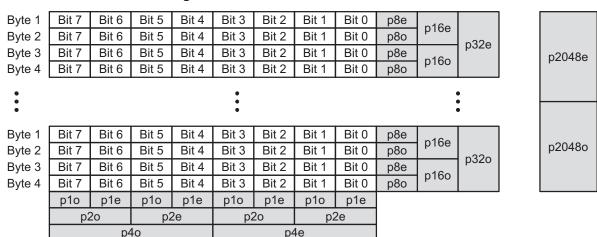

| 9  | ECC Value for 8-Bit NAND Flash                                       | 25 |

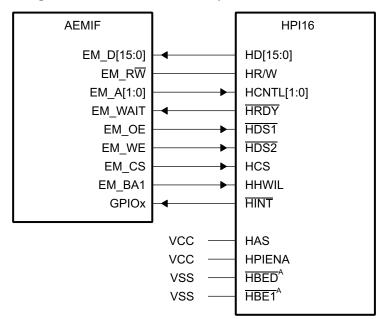

| 10 | EMIF to 16-Bit Multiplexed HPI16 Interface                           | 26 |

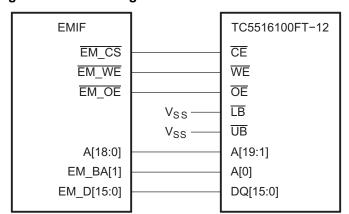

| 11 | Connecting the EMIF to the TC55V16100FT-12                           | 30 |

| 12 | Timing Waveform of an ASRAM Read                                     | 32 |

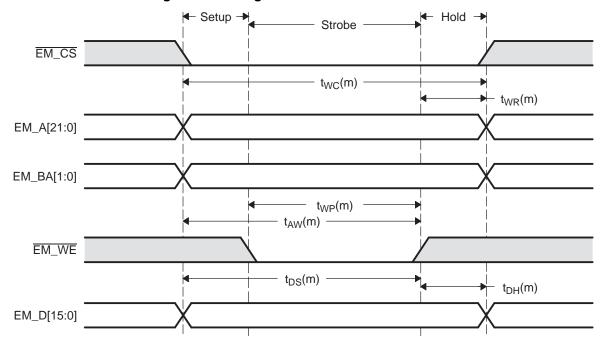

| 13 | Timing Waveform of an ASRAM Write                                    | 33 |

| 14 | Timing Waveform of an ASRAM Read with PCB Delays                     | 35 |

| 15 | Timing Waveform of an ASRAM Write with PCB Delays                    | 36 |

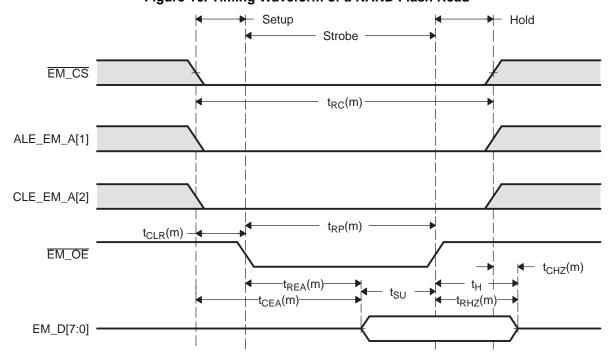

| 16 | Timing Waveform of a NAND Flash Read                                 | 41 |

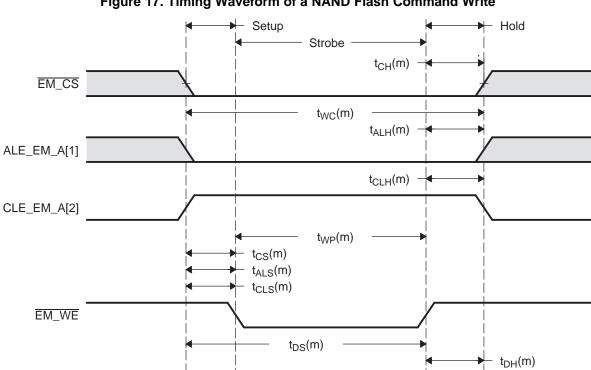

| 17 | Timing Waveform of a NAND Flash Command Write                        | 43 |

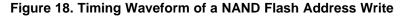

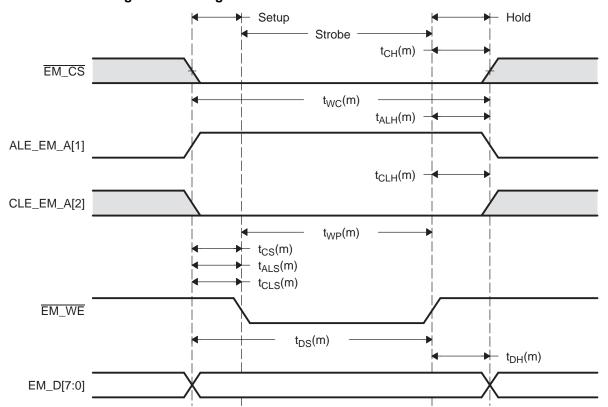

| 18 | Timing Waveform of a NAND Flash Address Write                        | 43 |

| 19 | Timing Waveform of a NAND Flash Data Write                           | 44 |

| 20 | Revision Code and Status Register (RCSR)                             | 49 |

| 21 | Asynchronous Wait Cycle Configuration Register (AWCCR)               | 50 |

| 22 | Asynchronous <i>n</i> Configuration Register (ACFG <i>n</i> )        | 52 |

| 23 | EMIF Interrupt Raw Register (EIRR)                                   | 53 |

| 24 | EMIF Interrupt Mask Register (EIMR)                                  | 54 |

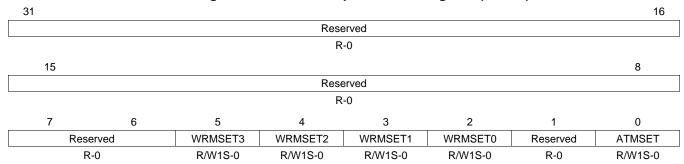

| 25 | EMIF Interrupt Mask Set Register (EIMSR)                             | 56 |

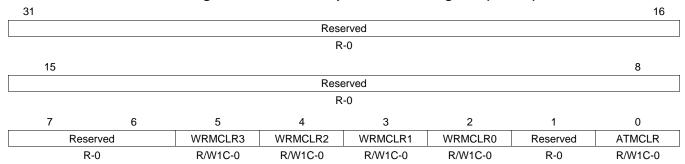

| 26 | EMIF Interrupt Mask Clear Register (EIMCR)                           | 58 |

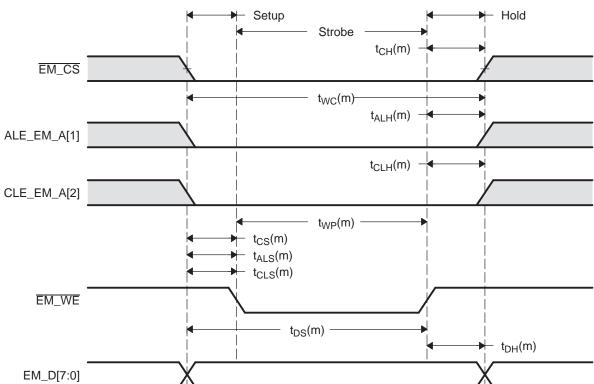

| 27 | NAND Flash Control Register (NANDFCR)                                | 60 |

| 28 | NAND Flash Status Register (NANDFSR)                                 | 61 |

| 29 | NAND Flash <i>n</i> ECC Register (NANDECC <i>n</i> )                 | 62 |

## **List of Tables**

| 1  | EMIF Pins                                                                        | 10 |

|----|----------------------------------------------------------------------------------|----|

| 2  | Behavior of EM_CS Signal Between Normal Mode and Select Strobe Mode              | 10 |

| 3  | Description of the Asynchronous Configuration Register (ACFGn)                   | 12 |

| 4  | Description of the Asynchronous Wait Cycle Configuration Register (AWCCR)        | 13 |

| 5  | Description of the EMIF Interrupt Mask Set Register (EIMSR)                      | 13 |

| 6  | Description of the EMIF Interrupt Mast Clear Register (EIMCR)                    | 13 |

| 7  | Asynchronous Read Operation in Normal Mode                                       | 14 |

| 8  | Asynchronous Write Operation in Normal Mode                                      | 16 |

| 9  | Asynchronous Read Operation in Select Strobe Mode                                | 18 |

| 10 | Asynchronous Write Operation in Select Strobe Mode                               | 20 |

| 11 | Description of the NAND Flash Control Register (NANDFCR)                         | 22 |

| 12 | Configuration For NAND Flash                                                     | 22 |

| 13 | EMIF Interrupt                                                                   | 28 |

| 14 | Interrupt Monitor and Control Bit Fields                                         | 28 |

| 15 | EMIF Input Timing Requirements                                                   | 31 |

| 16 | ASRAM Output Timing Characteristics                                              | 31 |

| 17 | ASRAM Input Timing Requirement for a Read                                        | 31 |

| 18 | ASRAM Input Timing Requirements for a Write                                      | 32 |

| 19 | ASRAM Timing Requirements With PCB Delays                                        | 34 |

| 20 | EMIF Timing Requirements for TC5516100FT-12 Example                              | 37 |

| 21 | ASRAM Timing Requirements for TC5516100FT-12 Example                             | 37 |

| 22 | Measured PCB Delays for TC5516100FT-12 Example                                   | 37 |

| 23 | Configuring A2CR for TC5516100FT-12 Example                                      | 39 |

| 24 | Recommended Margins                                                              | 39 |

| 25 | EMIF Read Timing Requirements                                                    |    |

| 26 | NAND Flash Read Timing Requirements                                              | 40 |

| 27 | NAND Flash Write Timing Requirements                                             | 42 |

| 28 | EMIF Timing Requirements for HY27UA081G1M Example                                | 45 |

| 29 | NAND Flash Timing Requirements for HY27UA081G1M Example                          |    |

| 30 | Configuring A1CR for HY27UA081G1M Example                                        |    |

| 31 | Configuring NANDFCR for HY27UA081G1M Example                                     |    |

| 32 | External Memory Interface (EMIF) Registers                                       |    |

| 33 | Revision Code and Status Register (RCSR) Field Descriptions                      | 49 |

| 34 | Asynchronous Wait Cycle Configuration Register (AWCCR) Field Descriptions        | 50 |

| 35 | Asynchronous <i>n</i> Configuration Register (ACFG <i>n</i> ) Field Descriptions | 52 |

| 36 | EMIF Interrupt Raw Register (EIRR) Field Descriptions                            | 53 |

| 37 | EMIF Interrupt Mask Register (EIMR) Field Descriptions                           | 54 |

| 38 | EMIF Interrupt Mask Set Register (EIMSR) Field Descriptions                      | 56 |

| 39 | EMIF Interrupt Mask Clear Register (EIMCR) Field Descriptions                    | 58 |

| 40 | NAND Flash Control Register (NANDFCR) Field Descriptions                         | 60 |

| 41 | NAND Flash Status Register (NANDFSR) Field Descriptions                          | 61 |

| 42 | NAND Flash n ECC Register (NANDECCn) Field Descriptions                          | 62 |

| 43 | Document Revision History                                                        | 63 |

## Read This First

#### **About This Manual**

This document describes the asynchronous external memory interface (EMIF) in the TMS320DM646x Digital Media System-on-Chip (DMSoC). The EMIF supports a glueless interface to a variety of external devices.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM646x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <a href="www.ti.com">www.ti.com</a>. Tip: Enter the literature number in the search box provided at <a href="www.ti.com">www.ti.com</a>.

The current documentation that describes the DM646x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="www.ti.com/c6000">www.ti.com/c6000</a>.

- <u>SPRUEP8</u> *TMS320DM646x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRUEP9 TMS320DM646x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem and a majority of the peripherals and external memories.

- SPRUEQ0 TMS320DM646x DMSoC Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

<u>SPRU871</u> — *TMS320C64x+ DSP Megamodule Reference Guide.* Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

# Asynchronous External Memory Interface (EMIF)

#### 1 Introduction

This document describes the operation of the asynchronous external memory interface (EMIF) in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

## 1.1 Purpose of the Peripheral

The purpose of this EMIF is to provide a means to connect to a variety of external devices including:

- NAND Flash

- Asynchronous devices including Flash and SRAM

- Host processor interfaces such as the host port interface (HPI) on a Texas Instruments Digital Signal Processor (DSP)

The most common use for the EMIF is to interface with both flash devices and SRAM devices. The *Example Configuration* section contains examples of operating the EMIF in this configuration.

#### 1.2 Features

The EMIF includes many features to enhance the ease and flexibility of connecting to external asynchronous devices. The EMIF features includes support for:

- 4 addressable chip select spaces of up to 32MB each

- 8-bit and 16-bit data bus widths

- Programmable cycle timings such as setup, strobe, and hold times as well as turnaround time

- Select strobe mode

- · Extended Wait mode

- NAND Flash ECC generation

- Connecting as a host to a TI DSP HPI interface

- Data bus parking

#### 1.3 Functional Block Diagram

Figure 1 illustrates the connections between the EMIF and its internal requesters, along with the external EMIF pins. Section 2.2 contains a description of the entities internal to the device that can send requests to the EMIF, along with their prioritization. Section 2.3 describes the EMIF's external pins and summarizes their purpose when interfacing with SDRAM and asynchronous devices.

SCR

EMIF

EM\_CS[5:2]

EM\_OE

EM\_RW

EM\_WAIT[5:2]

EM\_BA[1:0]

EM\_BA[1:0]

EM\_BA[22:0]

Master peripherals

Figure 1. EMIF Functional Block Diagram

#### 2 Architecture

This section provides details about the architecture and operation of the EMIF.

#### 2.1 Clock Control

The EMIF's internal clock is sourced from the SYSCLK3 clock domain of PLL controller 0 and cannot be sourced directly from an external input clock. The frequency of the SYSCLK3 clock domain is the PLL0 frequency divided by 4. Changes to the frequency of the input clock to PLL controller 0 and to the PLL controller 0 multiplier values alters the operating frequency of the EMIF. See the *TMS320DM646x DMSoC ARM Subsystem Reference Guide* (SPRUEP9) for more information on how to program the PLL controller.

### 2.2 EMIF Requests

Four different sources within the device can make requests to the EMIF. These requests consist of accesses to asynchronous memory and EMIF memory-mapped registers. Because the EMIF can process only one request at a time, a high performance switched central resource (SCR) exists to provide prioritized requests from the different sources to the EMIF. Each requester has a programmable priority value that may be configured in the System Module MSTPRIO register or in the EDMACC QUEPRI register. See the device-specific data manual for more information.

If a request is submitted from two or more sources simultaneously, the SCR will forward the highest priority request to the EMIF first. Upon completion of a request, the SCR again evaluates the pending requests and forwards the highest priority pending request to the EMIF.

#### 2.3 Signal Descriptions

Table 1 describes the function of each of the EMIF pins.

**Table 1. EMIF Pins**

| Pins(s)      | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EM_ A[22:0]  | 0   | EMIF address bus. These pins are used in conjunction with the EM_BA pins to form the address that is sent to the device.                                                                                                                                                                                                                                                                                                                                          |

| EM_BA[1:0]   | 0   | EMIF bank address. These pins are used in conjunction with the EM_A pins to form the address that is sent to the device.                                                                                                                                                                                                                                                                                                                                          |

| EM_CS[5:2]   | 0   | Active-low chip enable pin for asynchronous devices. These pins are meant to be connected to the chip-select pin of the attached asynchronous device.                                                                                                                                                                                                                                                                                                             |

| EM_D[15:0]   | I/O | EMIF data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EM_RW        | 0   | Read/Write select pin. This pin is high for the duration of an asynchronous read access cycle and low for the duration of an asynchronous write cycle.                                                                                                                                                                                                                                                                                                            |

| EM_OE        | 0   | Active-low pin enable for asynchronous devices. This pin provides a signal which is active-low during the strobe period of an asynchronous read access cycle.                                                                                                                                                                                                                                                                                                     |

| EM_WE        | 0   | Active-low write enable. This pin provides a signal which is active-low during the strobe period of an asynchronous write access cycle.                                                                                                                                                                                                                                                                                                                           |

| EM_WAIT[5:2] | I   | Wait input with programmable polarity. A connected asynchronous device can extend the strobe period of an access cycle by asserting the WAIT input to the EMIF as described in Section 2.5.8. To enable this functionality, the EW bit in the asynchronous configuration register (ACFGn) must be set to 1. In addition, the WPn bit in the asynchronous wait cycle configuration register (AWCCR) must be configured to define the polarity of the EM_WAITn pin. |

#### 2.4 Pin Multiplexing

The EMIF pins are multiplexed with other peripherals such as PCI, HPI, GPIO, and ATA. See the device-specific data manual for instructions on how to select the EMIF pins for proper operation.

#### 2.5 Asynchronous Controller and Interface

The EMIF easily interfaces to a variety of asynchronous devices including Flash and ASRAM. It can be operated in three major modes:

- Normal mode

- Select Strobe (SS) mode

- NAND Flash mode

The behavior of the  $\overline{EM\_CS}$  signal is the single difference between Normal mode and Select Strobe mode (see Table 2). In Normal mode, the  $\overline{EM\_CS}$  signal becomes active at the beginning of the setup period and remains active for the duration of the transfer. In Select Strobe mode, the  $\overline{EM\_CS}$  signal functions as a strobe signal, active only during the strobe period of an access.

In NAND Flash mode, the EMIF hardware is able to calculate the error correction code (ECC) for each 512 byte data transfer. In addition to the three modes of operation, the EMIF also provides configurable cycle timing parameters and an Extended Wait mode that allows the connected device to extend the strobe period of an access cycle. The following sections describe the features related to interfacing with external asynchronous devices.

Table 2. Behavior of EM\_CS Signal Between Normal Mode and Select Strobe Mode

| Mode          | Operation of EM_CS[5:2]                                 |

|---------------|---------------------------------------------------------|

| Normal        | Active during the entire asynchronous access cycle      |

| Select Strobe | Active only during the strobe period of an access cycle |

#### 2.5.1 Interfacing to Asynchronous Memory

Figure 2 shows the EMIF's external pins used in interfacing with an asynchronous device. Of special note is the connection between the EMIF and the external device's address bus. The EMIF address pin EM\_A[0] always provides the least significant bit of a 32-bit word address. Therefore, when interfacing to a 16-bit or 8-bit asynchronous device, the EM\_BA[1] and EM\_BA[0] pins provide the least-significant bits of the halfword or byte address, respectively. Figure 2 and Figure 3 show the mapping between the EMIF and the connected device's data and address pins for various programmed data bus widths. The data bus width may be configured in the asynchronous configuration register (ACFGn).

EMIF

EM\_CS[5:2]

EM\_WE

EM\_OE

EM\_RW

EM\_WAIT[5:2]

EM\_D[15:0]

EM\_A[22:0]

EM\_BA[1:0]

Figure 2. EMIF Asynchronous Interface

Figure 3. EMIF to 8-bit and 16-bit Memory Interfaces

a) EMIF to 8-bit memory interface

b) EMIF to 16-bit memory interface

#### 2.5.2 Programmable Asynchronous Parameters

The EMIF allows a high degree of programmability for shaping asynchronous accesses. The programmable parameters are:

- **Setup:** The time between the beginning of a memory cycle (address valid) and the activation of the output enable or write enable strobe

- Strobe: The time between the activation and deactivation of output enable or write enable strobe.

- **Hold:** The time between the deactivation of output enable or write enable strobe and the end of the cycle, which may be indicated by an address change or the deactivation of the EM\_CS signal.

Separate parameters are provided for read and write cycles. Each parameter is programmed in terms of EMIF clock cycles.

#### 2.5.3 Configuring the EMIF for Asynchronous Accesses

The operation of the EMIF's asynchronous interface can be configured by programming the appropriate memory-mapped registers. The reset value and bit position for each register field can be found in Section 4. The following tables list the programmable register fields and describe the purpose of each field. These registers should not be programmed while an asynchronous access is in progress. The transfer following a write to these registers will use the new configuration.

Table 3 describes the asynchronous configuration register (ACFGn). There are four ACFGns. Each chip select space has a dedicated ACFGn. This allows each chip select space to be programmed independently to interface to different asynchronous memory types.

Table 3. Description of the Asynchronous Configuration Register (ACFGn)

| Parameter         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS                | Select Strobe mode. This bit selects the EMIF's mode of operation in the following way:                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | <ul> <li>SS = 0 selects Normal mode. EM_CS is active for duration of access.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | <ul> <li>SS = 1 selects Select Strobe mode. EM_CS acts as a strobe.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| EW                | Extended Wait mode enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | <ul> <li>EW = 0 disables Extended Wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | • EW = 1 enables Extended Wait mode When set to 1, the EMIF enables its Extended Wait mode in which the strobe width of an access cycle can be extended in response to the assertion of the EM_WAIT[5:2] pins. The WPn bit in the asynchronous wait cycle configuration register (AWCCR) controls the polarity of the EM_WAITn pin. See Section 2.5.8 for more details on this mode of operation.                                                                                      |

| W_SETUP/R_SETUP   | Read/Write setup widths.  These fields define the number of EMIF clock cycles of setup time for the address pins (EM_A and EM_BA) and asynchronous chip enable (EM_CS) before the read strobe pin (READ_OE) or write strobe pin (WRITE_WE) falls, minus 1 cycle. For writes, the W_SETUP field also defines the setup time for the data pins (EM_D). Refer to the datasheet of the external asynchronous device to determine the appropriate setting for this field.                   |

| W_STROBE/R_STROBE | Read/Write strobe widths.  These fields define the number of EMIF clock cycles between the falling and rising of the read strobe pin (READ_OE) or write strobe pin (WRITE_WE), minus 1 cycle. If Extended Wait mode is enabled by setting the EW bit in the asynchronous configuration register (ACFGn), these fields must be set to a value greater than zero. Refer to the datasheet of the external asynchronous device to determine the appropriate setting for this field.        |

| W_HOLD/R_HOLD     | Read/Write hold widths.  These fields define the number of EMIF clock cycles of hold time for the address pins (EM_A and EM_BA) and asynchronous chip enable (EM_CS) after the read strobe pin (READ_OE) or write strobe pin (WRITE_WE) rises, minus 1 cycle. For writes, the W_HOLD field also defines the hold time for the data pins (EM_D). Refer to the datasheet of the external asynchronous device to determine the appropriate setting for this field.                        |

| TA                | Minimum turnaround time.  This field defines the minimum number of EMIF clock cycles between the end of one asynchronous access and the start of another, minus 1 cycle. This delay is not incurred when a read is followed by a read, or a write is followed by a write to the same chip select space. The purpose of this feature is to avoid contention on the bus. Refer to the datasheet of the external asynchronous device to determine the appropriate setting for this field. |

Table 3. Description of the Asynchronous Configuration Register (ACFGn) (continued)

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIZE     | Asynchronous Device Bus Width.  This field determines the data bus width of the asynchronous interface in the following way:                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | ASIZE = 0 selects an 8-bit bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | <ul> <li>ASIZE = 1 selects a 16-bit bus         The configuration of ASIZE determines the function of the EM_A and EM_BA pins as described in Section 2.5.1. This field also determines the number of external accesses required to fulfill a request generated by one of the sources mentioned in Section 2.2. For example, a request for a 32-bit word would require four external access when ASIZE = 0h. Refer to the datasheet of the external asynchronous device to determine the appropriate setting for this field.     </li> </ul> |

### Table 4. Description of the Asynchronous Wait Cycle Configuration Register (AWCCR)

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WPn       | WAIT Polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | <ul> <li>WPn = 0 selects active-low polarity</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | <ul> <li>WPn = 1 selects active-high polarity</li> <li>When set to 1, the EMIF will wait if the EM_WAITn pin is high. When cleared to 0, the EMIF will wait if the EM_WAITn pin is low. The EMIF must have the Extended Wait mode enabled (EW bit in the asynchronous configuration register (ACFGn) is set to 1) for the EM_WAITn pin to affect the width of the strobe period.</li> </ul>                                                                               |

| MEWC      | Maximum Extended Wait Cycles. This field configures the number of EMIF clock cycles the EMIF will wait for the EM_WAIT n pin to be deactivated during the strobe period of an access cycle. The maximum number of EMIF clock cycles the EMIF will wait is determined by the following formula:                                                                                                                                                                            |

|           | Maximum Extended Wait Cycles = (MEWC + 1) x 16                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | If the EM_WAITn pin is not deactivated within the time specified by this field, the EMIF resumes the access cycle, registering whatever data is on the bus and preceding to the hold period of the access cycle. This situation is referred to as an asynchronous timeout. An asynchronous timeout generates an interrupt if it has been enabled in the EMIF interrupt mask set register (EIMSR). Refer to Section 2.5.11 for more information about the EMIF interrupts. |

## Table 5. Description of the EMIF Interrupt Mask Set Register (EIMSR)

| Parameter | Description                                                                                                                      |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|

| WRMSETn   | Wait Rise Mask Set. Writing a 1 enables an interrupt to be generated when a rising edge on EM_WAITn occurs.                      |  |

| ATMSET    | Asynchronous Timeout Mask Set. Writing a 1 to this bit enables an interrupt to be generated when an asynchronous timeout occurs. |  |

## Table 6. Description of the EMIF Interrupt Mast Clear Register (EIMCR)

| Parameter | Description                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRMCLRn   | Wait Rise Mask Clear. Writing a 1 to this bit disables the interrupt, clearing the WRMSETn bit in the EMIF interrupt mask set register (EIMSR).           |

| ATMCLR    | Asynchronous Timeout Mask Clear. Writing a 1 to this bit disables the interrupt, clearing the ATMSET bit in the EMIF interrupt mask set register (EIMSR). |

#### 2.5.4 Read and Write Operations in Normal Mode

Normal mode is the asynchronous interface's default mode of operation. The Normal mode is selected when the SS bit in the asynchronous configuration register (ACFGn) is cleared to 0. In this mode, the EM\_CS signal operates as a chip enable signal, active throughout the duration of the memory access.

#### 2.5.4.1 Asynchronous Read Operations (Normal Mode)

An asynchronous read is performed when any of the requesters mentioned in Section 2.2 request a read from the attached asynchronous memory. In the event that the read request cannot be serviced by a single access cycle to the external device, multiple access cycles will be performed by the EMIF until the entire request is fulfilled. The details of an asynchronous read operation in Normal mode are described in Table 7 and an example timing diagram of a basic read operation is shown in Figure 4.

**NOTE:** During the entirety of an asynchronous read operation, the  $\overline{WRITE\_WE}$  and  $EM\_R\overline{W}$  pins are driven high.

Table 7. Asynchronous Read Operation in Normal Mode

| Time Interval     | Pin Activity in WE Strobe Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Turnaround period | Once the EMIF receives a read request, the EMIF waits for the programmed number of turn-around cycles before proceeding to the setup period of the operation. The number of wait cycles is taken directly from the TA field of the asynchronous configuration register (ACFGn). There are two exceptions to this rule:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | <ul> <li>If the current read operation was directly proceeded by another read operation to the same CS space, no<br/>turnaround cycles are inserted.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | If the current read operation was not directly proceeded by a read operation to the same CS space and the TA field has been cleared to 0, one turn-around cycle will be inserted.  After the TAILS have reided for the turn-around evaluations and the tail of the control of t |

|                   | After the EMIF has waited for the turnaround cycles to complete, it proceeds to the setup period of the operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Start of setup    | At the beginning of the setup period:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| period            | <ul> <li>The setup, strobe, and hold values are set according to the R_SETUP, R_STROBE, and R_HOLD values<br/>in ACFGn.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | <ul> <li>The address pins EM_A and EM_BA become valid</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | <ul> <li>EM_CS falls to enable the external device (if not already low from a previous operation)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Start of strobe   | At the beginning of the strobe period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| period            | READ_OE falls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Start of hold     | At the beginning of the hold period:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| period            | READ_OE rises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | The EMIF samples the data on the EM_D bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| End of hold       | At the end of the hold period:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| period            | The address pins EM_A and EM_BA become invalid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | <ul> <li>EM_CS rises (if no more operations are required to complete the current request)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   | The EMIF will be required to issue additional read operations to a device with a small data bus width in order to complete an entire word access. In this case, the EMIF immediately re-enters the setup period to begin another operation without incurring the turn-round cycle delay. The setup, strobe, and hold values are not updated in this case. If the entire word access has been completed, the EMIF returns to its previous state unless another asynchronous request has been submitted and is currently the highest priority task. If this is the case, the EMIF instead enters directly into the turnaround period for the pending read or write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### 2.5.4.2 Asynchronous Write Operations (Normal Mode)

An asynchronous write is performed when any of the requesters mentioned in Section 2.2 request a write to asynchronous memory. In the event that the write request cannot be serviced by a single access cycle to the external device, multiple access cycles will be performed by the EMIF until the entire request is fulfilled. The details of an asynchronous write operation in Normal mode are described in Table 8 and an example timing diagram of a basic write operation is shown in Figure 5.

**NOTE:** During the entirety of an asynchronous write operation, the EM\_OE pin is driven high.

Table 8. Asynchronous Write Operation in Normal Mode