# Keystone II Architecture DDR3 Memory Controller

# **User's Guide**

Literature Number: SPRUHN7C October 2013–Revised March 2015

# **Contents**

| Prefa | ace    |                                                                      | 9  |

|-------|--------|----------------------------------------------------------------------|----|

| 1     | Introd | duction                                                              | 11 |

|       | 1.1    | Purpose of the Peripheral                                            |    |

|       | 1.2    | Features                                                             |    |

|       | 1.3    | Industry Standard(s) Compliance Statement                            | 12 |

| 2     | Perip  | heral Architecture                                                   | 14 |

|       | 2.1    | Clock Interface                                                      | 15 |

|       | 2.2    | SDRAM Memory Map                                                     | 15 |

|       | 2.3    | Signal Descriptions                                                  | 15 |

|       | 2.4    | Protocol Descriptions                                                | 16 |

|       |        | 2.4.1 Mode Register Set (MRS or EMRS)                                | 17 |

|       |        | 2.4.2 Refresh Mode                                                   | 18 |

|       |        | 2.4.3 Activation                                                     | 18 |

|       |        | 2.4.4 Deactivation                                                   | 18 |

|       |        | 2.4.5 READ Command                                                   | 18 |

|       |        | 2.4.6 Write (WR) Command                                             | 19 |

|       | 2.5    | Address Mapping                                                      | 20 |

|       | 2.6    | DDR3 Memory Controller Interface                                     | 23 |

|       |        | 2.6.1 Arbitration                                                    | 24 |

|       |        | 2.6.2 Command Starvation                                             | 25 |

|       |        | 2.6.3 Possible Race Condition                                        | 25 |

|       |        | 2.6.4 Class of Service                                               | 25 |

|       | 2.7    | Refresh Scheduling                                                   | 26 |

|       | 2.8    | Self-Refresh Mode                                                    |    |

|       |        | 2.8.1 Extended Temperature Range                                     | 27 |

|       | 2.9    | Reset Considerations                                                 | 27 |

|       | 2.10   | Turnaround Time                                                      | 28 |

|       | 2.11   | DDR3 SDRAM Memory Initialization                                     | 28 |

|       |        | 2.11.1 DDR3 Initialization Sequence                                  | 30 |

|       | 2.12   | Leveling                                                             | 30 |

|       | 2.13   | Interrupt Support                                                    | 30 |

|       | 2.14   | EDMA Event Support                                                   | 30 |

|       | 2.15   |                                                                      | 30 |

|       | 2.16   | ECC                                                                  |    |

|       |        | 2.16.1 ECC Feature Enhancements                                      |    |

|       |        | 2.16.1.1 Read-modify-write                                           | 31 |

|       |        | 2.16.1.2 Logging 1-bit ECC Error Address                             |    |

|       |        | 2.16.1.3 Counting the Number of 1-bit ECC Errors                     |    |

|       |        | 2.16.1.4 Diagnosing the Data bus bit on which 1-bit ECC Errors Occur |    |

|       |        | 2.16.1.5 Logging 2-bit ECC Error Address                             |    |

|       | 2.17   | Data Bus Obfuscation                                                 |    |

|       | 2.18   | Power Management                                                     | 34 |

|       |        | 2.18.1 SDRAM Self-Refresh Mode                                       | 34 |

|       |        | 2.18.2 SDRAM Power-Down Mode                                         | 34 |

|       | 2.19   | Performance Monitoring                                               | 34 |

| www | .τι. | com |

|-----|------|-----|

|     |      |     |

| 3 | Using            | the DDR3 Memory Controller                                                     | 37  |

|---|------------------|--------------------------------------------------------------------------------|-----|

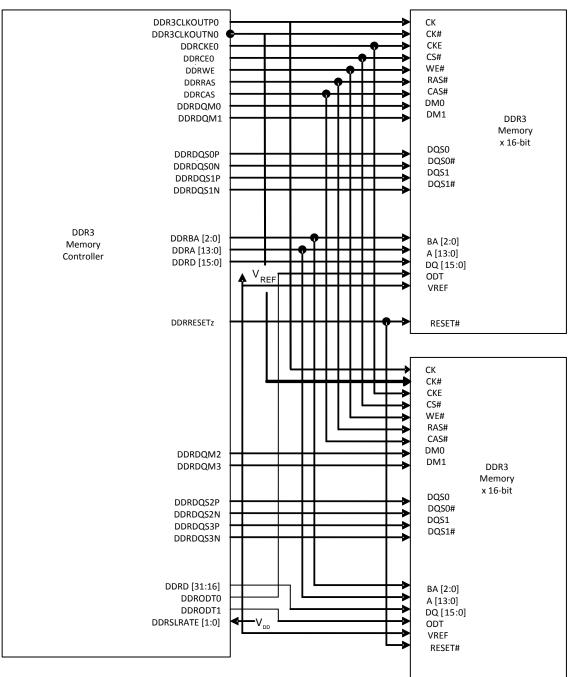

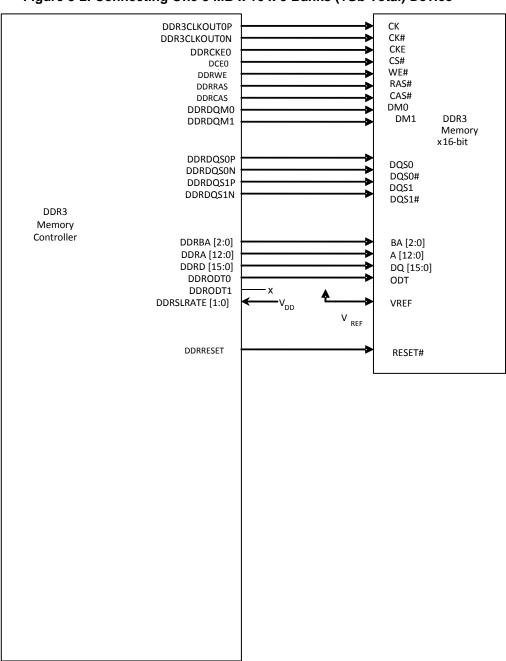

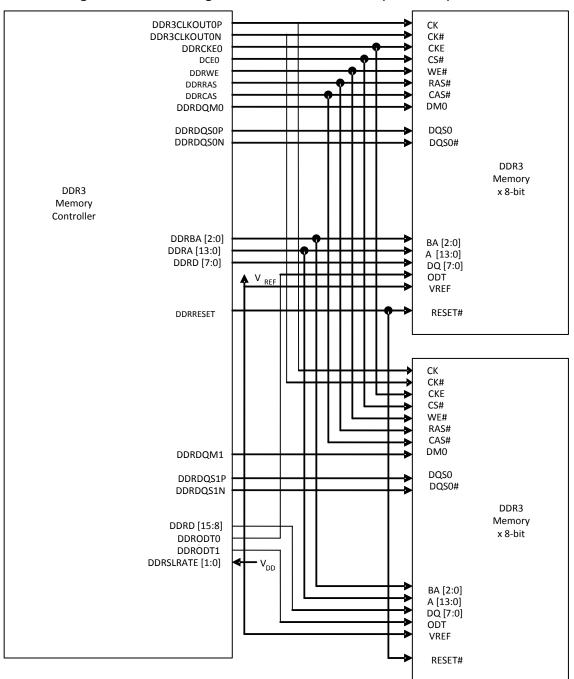

|   | 3.1              | Connecting the DDR3 Memory Controller to DDR3 SDRAM                            | 38  |

|   | 3.2              | Configuring DDR3 Memory Controller Registers to Meet DDR3 SDRAM Specifications | 42  |

|   |                  | 3.2.1 Programming the SDRAM Configuration Register (SDCFG)                     | 42  |

|   |                  | 3.2.2 Programming the SDRAM Refresh Control Register (SDRFC)                   | 42  |

|   |                  | 3.2.3 Configuring SDRAM Timing Registers (SDTIM1, SDTIM2, SDTIM3, SDTIM4)      |     |

| 4 | נסחח             | Memory Controller Registers                                                    |     |

| 4 |                  | Module ID and Revision Register (MIDR)                                         |     |

|   | 4.1              | - · · ·                                                                        |     |

|   | 4.2              | DDR3 Memory Controller Status Register (STATUS)                                |     |

|   | 4.3              | SDRAM Configuration Register (SDCFG)                                           |     |

|   | 4.4              | SDRAM Refresh Control Register (SDRFC)                                         |     |

|   | 4.5              | SDRAM Timing 1 (SDTIM1) Register                                               |     |

|   | 4.6              | SDRAM Timing 2 (SDTIM2) Register                                               |     |

|   | 4.7              | SDRAM Timing 3 (SDTIM3) Register                                               |     |

|   | 4.8              | SDRAM Timing 4 (SDTIM4) Register                                               |     |

|   | 4.9              | Power Management Control Register (PMCTL)                                      | 59  |

|   | 4.10             | VBUSM Configuration Register (VBUSM_CONFIG)                                    | 61  |

|   | 4.11             | Performance Counter 1 Register (PERF_CNT_1)                                    | 62  |

|   | 4.12             | Performance Counter 2 Register (PERF_CNT_2)                                    | 63  |

|   | 4.13             | Performance Counter Config Register (PERF_CNT_CFG)                             | 64  |

|   | 4.14             | Performance Counter Master Region Select Register (PERF_CNT_SEL)               |     |

|   | 4.15             | Performance Counter Time Register (PERF_CNT_TIM)                               |     |

|   | 4.16             | Interrupt Raw Status Register (IRQSTATUS_RAW_SYS)                              |     |

|   | 4.17             | Interrupt Status Register (IRQSTATUS_SYS)                                      |     |

|   | 4.18             | Interrupt Enable Set Register (IRQSTATUS_SET_SYS)                              |     |

|   | 4.19             | Interrupt Enable Clear Register (IRQSTATUS_CLR_SYS)                            |     |

|   | 4.20             | SDRAM Output Impedance Calibration Configuration Register (ZQCFG)              |     |

|   | 4.21             | Priority to Class-Of-Service Mapping Register (PRI_COS_MAP)                    |     |

|   | 4.22             | Master ID to Class-Of-Service 1 Mapping Register (MSTID_COS_1_MAP)             |     |

|   | 4.22             | Master ID to Class-Of-Service 2 Mapping Register (MSTID_COS_2_MAP)             |     |

|   | 4.23<br>4.24     | ECC Control Register (ECCCTL)                                                  |     |

|   |                  |                                                                                |     |

|   | 4.25             | ECC Address Range 1 Register (ECCADDR1)                                        |     |

|   | 4.26             | ECC Address Range 2 Register (ECCADDR2)                                        |     |

|   | 4.27             | Read Write Execution Threshold Register (RWTHRESH)                             |     |

|   | 4.28             | 1-Bit ECC Error Count Register (ONE_BIT_ECC_ERR_CNT)                           |     |

|   | 4.29             | 1-Bit ECC Error Threshold Register (ONE_BIT_ECC_ERR_THRSH)                     |     |

|   | 4.30             | 1-Bit ECC Error Distribution 1 Register (ONE_BIT_ECC_ERR_DIST_1)               |     |

|   | 4.31             | 1-Bit ECC Error Address Log Register (ONE_BIT_ECC_ERR_ADDR_LOG)                |     |

|   | 4.32             | 2-Bit ECC Error Address Log Register (TWO_BIT_ECC_ERR_ADDR_LOG)                |     |

|   | 4.33             | 1-Bit ECC Error Distribution 2 Register (ONE_BIT_ECC_ERR_DIST_2)               |     |

|   | 4.34             | PHY Initialization Register (PIR)                                              |     |

|   | 4.35             | PHY General Configuration Register 0 (PGCR0)                                   | 87  |

|   | 4.36             | PHY General Configuration Register 1 (PGCR1)                                   | 89  |

|   | 4.37             | PHY General Configuration Register 2 (PGCR2)                                   | 91  |

|   | 4.38             | PHY General Status Register 0 (PGSR0)                                          | 92  |

|   | 4.39             | PHY General Status Register 1 (PGSR1)                                          | 94  |

|   | 4.40             | PLL Control Register (PLLCR)                                                   | 95  |

|   | 4.41             | PHY Timing Register 0 (PTR0)                                                   |     |

|   | 4.42             | PHY Timing Register 1 (PTR1)                                                   |     |

|   | 4.43             | PHY Timing Register 2 (PTR2)                                                   |     |

|   | 4.44             | PHY Timing Register 3 (PTR3)                                                   |     |

|   | 4.45             |                                                                                | 100 |

|   | 4.46             | AC I/O Configuration Register (ACIOCR)                                         |     |

|   | <del>т.+</del> 0 |                                                                                | 101 |

| w |  |  |  |  |

|---|--|--|--|--|

|   |  |  |  |  |

|   |  |  |  |  |

|   |  |  |  |  |

| 4.47              | DATX8 Common Configuration Register (DXCCR)              | 102 |

|-------------------|----------------------------------------------------------|-----|

| 4.48              | DRAM Configuration Register (DCR)                        |     |

| 4.49              | DRAM Timing Parameters Register 0 (DTPR0)                | 105 |

| 4.50              | DRAM Timing Parameters Register 1 (DTPR1)                | 106 |

| 4.51              | DRAM Timing Parameters Register 2 (DTPR2)                | 107 |

| 4.52              | Mode Register 0 (MR0)                                    | 108 |

| 4.53              | Mode Register 1 (MR1)                                    | 110 |

| 4.54              | Mode Register 2 (MR2)                                    | 112 |

| 4.55              | Mode Register 3 (MR3)                                    | 113 |

| 4.56              | ODT Configuration Register (ODTCR)                       | 114 |

| 4.57              | Data Training Configuration Register (DTCR)              | 115 |

| 4.58              | Impedance Control Register 0 (ZQnCR0)                    | 116 |

| 4.59              | Impedance Control Register 1 (ZQnCR1)                    |     |

| 4.60              | Impedance Status Register 0 (ZQnSR0)                     |     |

| 4.61              | Impedance Status Register 1 (ZQnSR1)                     |     |

| 4.62              | DATX8 General Configuration Register (DXnGCR)            |     |

| 4.63              | DATX8 General Status Register 0 (DXnGSR0)                | 122 |

| 4.64              | DATX8 General Status Register 2 (DXnGSR2)                |     |

| 4.65              | DATX8 Local Calibrated Delay Line Register 0 (DXnLCDLR0) |     |

| 4.66              | DATX8 Local Calibrated Delay Line Register 1 (DXnLCDLR1) |     |

| 4.67              | DATX8 Local Calibrated Delay Line Register 2 (DXnLCDLR2) |     |

| 4.68              | DATX8 Master Delay Line Register (DXnMDLR)               | 127 |

| 4.69              | DATX8 General Timing Register (DXnGTR)                   | 128 |

| <b>Revision H</b> | istory                                                   | 130 |

| <b>Revision H</b> | istory                                                   | 130 |

# List of Figures

| 2-1.  | DDR3 Memory Control Signals                                        | 15         |

|-------|--------------------------------------------------------------------|------------|

| 2-2.  | READ Command                                                       | 19         |

| 2-3.  | WRITE Command                                                      | 19         |

| 2-4.  | Logical Address-to-DDR3 SDRAM Address Map (EBANK=0)                | 22         |

| 2-5.  | DDR3 SDRAM Column, Row, and Bank Access (EBANK=0)                  | 22         |

| 2-6.  | DDR3 Memory Controller FIFO Block Diagram                          | 23         |

| 2-7.  | Data Bus Obfuscation                                               | 33         |

| 3-1.  | Connecting Two 16 MB x 16 x 8 Banks (4Gb Total) Devices            | 39         |

| 3-2.  | Connecting One 8 MB x 16 x 8 Banks (1Gb Total) Device              | 40         |

| 3-3.  | Connecting Two 16 MB x 8 x 8 Banks (2Gb Total) Devices             | 41         |

| 4-1.  | Module ID and Revision Register (MIDR)                             | 50         |

| 4-2.  | DDR3 Memory Controller Status Register (STATUS)                    | 51         |

| 4-3.  | SDRAM Configuration Register (SDCFG)                               | 52         |

| 4-4.  | SDRAM Refresh Control Register (SDRFC)                             | 54         |

| 4-5.  | SDRAM Timing 1 (SDTIM1) Register                                   | 55         |

| 4-6.  | SDRAM Timing 2 (SDTIM2) Register                                   | 56         |

| 4-7.  | SDRAM Timing 3 (SDTIM3) Register                                   | 57         |

| 4-8.  | SDRAM Timing 4 (SDTIM4) Register                                   | 58         |

| 4-9.  | Power Management Control Register (PMCTL)                          | 59         |

| 4-10. | VBUSM Configuration Register (VBUSM_CONFIG)                        | 61         |

| 4-11. | Performance Counter 1 Register (PERF_CNT_1)                        | 62         |

| 4-12. | Performance Counter 2 Register (PERF_CNT_2)                        | 63         |

| 4-13. | Performance Counter Config Register (PERF_CNT_CFG)                 | <b>6</b> 4 |

| 4-14. | Performance Counter Master Region Select Register (PERF_CNT_SEL)   | 65         |

| 4-15. | Performance Counter Time Register (PERF_CNT_TIM)                   | 66         |

| 4-16. | Interrupt Raw Status Register (IRQSTATUS_RAW_SYS)                  | 67         |

| 4-17. | Interrupt Status Register (IRQSTATUS_SYS)                          |            |

| 4-18. | Interrupt Enable Set Register (IRQSTATUS_SET_SYS)                  | <b>6</b> 9 |

| 4-19. | Interrupt Enable Clear Register (IRQSTATUS_CLR_SYS)                | 70         |

| 4-20. | SDRAM Output Impedance Calibration Configuration Register (ZQCFG)  |            |

| 4-21. | Priority to Class-Of-Service Mapping Register (PRI_COS_MAP)        | 72         |

| 4-22. | Master ID to Class-Of-Service 1 Mapping Register (MSTID_COS_1_MAP) |            |

| 4-23. | Master ID to Class-Of-Service 2 Mapping Register (MSTID_COS_2_MAP) | 74         |

| 4-24. | ECC Control Register (ECCCTL)                                      | 75         |

| 4-25. | ECC Address Range 1 Register (ECCADDR1)                            | 76         |

| 4-26. | ECC Address Range 2Register (ECCADDR2)                             | 77         |

| 4-27. | Read Write Execution Threshold Register (RWTHRESH)                 | 78         |

| 4-28. | 1-Bit ECC Error Count Register (ONE_BIT_ECC_ERR_CNT)               |            |

| 4-29. | 1-Bit ECC Error Threshold Register (ONE_BIT_ECC_ERR_THRSH)         | 80         |

| 4-30. | 1-Bit ECC Error Distribution 1 Register (ONE_BIT_ECC_ERR_DIST_1)   |            |

| 4-31. | 1-Bit ECC Error Address Log Register (ONE_BIT_ECC_ERR_ADDR_LOG)    | 82         |

| 4-32. | 2-Bit ECC Error Address Log Register (TWO_BIT_ECC_ERR_ADDR_LOG)    |            |

| 4-33. | 1-Bit ECC Error Distribution 2 Register (ONE_BIT_ECC_ERR_DIST_2)   | 84         |

| 4-34. | PHY Initialization Register (PIR)                                  |            |

| 4-35. | PHY General Configuration Register 0 (PGCR0)                       | 87         |

| 4-36. | PHY General Configuration Register 1 (PGCR1)                       |            |

| 4-37. | PHY General Configuration Register 2 (PGCR2)                       | 91         |

|       |                                                                    |            |

| w | ww | .ti. | com |

|---|----|------|-----|

|   |    |      |     |

| 4-38. | PHY General Status Register 0 (PGSR0)                    | 92  |

|-------|----------------------------------------------------------|-----|

| 4-39. | PHY General Status Register 1 (PGSR1)                    | 94  |

| 4-40. | PLL Control Register (PLLCR)                             | 95  |

| 4-41. | PHY Timing Register 0 (PTR0)                             | 96  |

| 4-42. | PHY Timing Register 1 (PTR1)                             | 97  |

| 4-43. | PHY Timing Register 2 (PTR2)                             | 98  |

| 4-44. | PHY Timing Register 3 (PTR3)                             | 99  |

| 4-45. | PHY Timing Register 4 (PTR4)                             | 100 |

| 4-46. | AC I/O Configuration Register (ACIOCR)                   | 101 |

| 4-47. | DATX8 Common Configuration Register (DXCCR)              | 102 |

| 4-48. | DRAM Configuration Register (DCR)                        | 104 |

| 4-49. | DRAM Timing Parameters Register 0 (DTPR0)                | 105 |

| 4-50. | DRAM Timing Parameters Register 1 (DTPR1)                | 106 |

| 4-51. | DRAM Timing Parameters Register 2 (DTPR2)                | 107 |

| 4-52. | Mode Register 0 (MR0)                                    | 108 |

| 4-53. | Mode Register 1 (MR1)                                    | 110 |

| 4-54. | Mode Register 2 (MR2)                                    | 112 |

| 4-55. | Mode Register 3 (MR3)                                    | 113 |

| 4-56. | ODT Configuration Register (ODTCR)                       | 114 |

| 4-57. | Data Training Configuration Register (DTCR)              | 115 |

| 4-58. | Impedance Control Register 0 (ZQnCR0)                    | 116 |

| 4-59. | Impedance Control Register 1 (ZQnCR1)                    | 117 |

| 4-60. | Impedance Status Register 0 (ZQnSR0)                     | 118 |

| 4-61. | Impedance Status Register 1 (ZQnSR1)                     | 119 |

| 4-62. | DATX8 General Configuration Register (DXnGCR)            | 120 |

| 4-63. | DATX8 General Status Register 0 (DXnGSR0)                | 122 |

| 4-64. | DATX8 General Status Register 2 (DXnGSR2)                | 123 |

| 4-65. | DATX8 Local Calibrated Delay Line Register 0 (DXnLCDLR0) | 124 |

| 4-66. | DATX8 Local Calibrated Delay Line Register 1 (DXnLCDLR1) | 125 |

| 4-67. | DATX8 Local Calibrated Delay Line Register 2 (DXnLCDLR2) | 126 |

| 4-68. | DATX8 Master Delay Line Register (DXnMDLR)               | 127 |

| 4-69. | DATX8 General Timing Register (DXnGTR)                   | 128 |

# List of Tables

| 2-1.  | DDR3 Memory Controller Signal Descriptions                                            | 15 |

|-------|---------------------------------------------------------------------------------------|----|

| 2-2.  | DDR3 SDRAM Commands                                                                   | 16 |

| 2-3.  | Truth Table for DDR3 SDRAM Commands                                                   | 17 |

| 2-4.  | Bank Configuration Register Fields for Address Mapping                                | 20 |

| 2-5.  | Logical Address-to-SDRAM Address Mapping                                              | 21 |

| 2-6.  | DDR3 Memory Controller FIFO Description                                               | 23 |

| 2-7.  | Device and DDR3 Memory Controller Reset Relationship                                  | 27 |

| 2-8.  | Turnaround Time                                                                       | 28 |

| 2-9.  | DDR3 SDRAM Extended Mode Register 2 Configuration                                     | 29 |

| 2-10. | DDR3 SDRAM Extended Mode Register 1 Configuration                                     | 29 |

| 2-11. | DDR3 SDRAM Mode Register 0 Configuration                                              | 29 |

| 2-12. | Performance Counter Filter Configuration                                              | 35 |

| 3-1.  | SDCFG Configuration                                                                   | 42 |

| 3-2.  | DDR3 Memory Refresh Specification                                                     | 42 |

| 3-3.  | See the register section for the SDTIM* register where the field exists               | 43 |

| 3-4.  | See the register section for the SDTIM* register where the field exists               | 44 |

| 3-5.  | See the register section for the SDTIM* register where the field exists               | 44 |

| 4-1.  | DDR3 Memory Controller Registers (See datasheet memory map for base address)          | 46 |

| 4-2.  | DDR3 PHY Registers (See device datasheet for base address)                            | 47 |

| 4-3.  | Module ID and Revision Register (MIDR) Field Descriptions                             | 50 |

| 4-4.  | DDR3 Memory Controller Status Register (STATUS) Field Descriptions                    |    |

| 4-5.  | SDRAM Configuration Register (SDCFG) Field Descriptions                               |    |

| 4-6.  | SDRAM Refresh Control (SDRFC) Register Field Descriptions                             |    |

| 4-7.  | SDRAM Timing 1 (SDTIM1) Register Field Descriptions                                   |    |

| 4-8.  | SDRAM Timing 2 (SDTIM2) Register Field Descriptions                                   |    |

| 4-9.  | SDRAM Timing 3 (SDTIM3) Register Field Descriptions                                   |    |

| 4-10. | SDRAM Timing 4 (SDTIM4) Register Field Descriptions                                   |    |

| 4-11. | Power Management Control Register (PMCTL) Field Descriptions                          |    |

| 4-12. | VBUSM Configuration Register (VBUSM_CONFIG) Field Descriptions                        |    |

| 4-13. | Performance Counter 1 Register (PERF_CNT_1) Field Descriptions                        |    |

| 4-14. | Performance Counter 2 Register (PERF_CNT_2) Field Descriptions                        |    |

| 4-15. | Performance Counter Config Register (PERF_CNT_CFG) Field Descriptions                 |    |

| 4-16. | Performance Counter Master Region Select Register (PERF_CNT_SEL) Field Descriptions   |    |

| 4-17. | Performance Counter Time Register (PERF_CNT_TIM) Field Descriptions                   |    |

| 4-18. | Interrupt Raw Status Register (IRQSTATUS_RAW_SYS) Field Descriptions                  |    |

| 4-19. | Interrupt Status Register (IRQSTATUS_SYS) Field Descriptions                          |    |

| 4-20. | Interrupt Enable Set Register (IRQSTATUS_SET_SYS) Field Descriptions                  |    |

| 4-21. | Interrupt Enable Clear Register (IRQSTATUS_CLR_SYS) Field Descriptions                |    |

| 4-22. | SDRAM Output Impedance Calibration Configuration Register (ZQCFG) Field Descriptions  |    |

| 4-23. | Priority to Class-Of-Service Mapping Register (PRICOSMAP) Field Descriptions          |    |

| 4-24. | Master ID to Class-Of-Service Mapping 1 Register (MSTID_COS_1_MAP) Field Descriptions |    |

| 4-25. | Master ID to Class-Of-Service Mapping 2 Register (MSTID_COS_2_MAP) Field Descriptions |    |

| 4-26. | ECC Control Register (ECCCTL) Field Descriptions                                      |    |

| 4-27. | ECC Address Range 1 Register Field Descriptions                                       |    |

| 4-28. | ECC Address Range 2 Register Field Descriptions                                       |    |

| 4-29. | Read Write Execution Threshold Register (RWTHRESH) Field Descriptions                 |    |

| 4-30. | 1-Bit ECC Error Count Register Field Descriptions                                     | 79 |

| 4-31. | 1-Bit ECC Error Threshold Register (ONE_BIT_ECC_ERR_THRSH) Field Descriptions       | 80  |

|-------|-------------------------------------------------------------------------------------|-----|

| 4-32. | 1-Bit ECC Error Distribution 1 Register (ONE_BIT_ECC_ERR_DIST_1) Field Descriptions | 81  |

| 4-33. | 1-Bit ECC Error Address Log Register (ONE_BIT_ECC_ERR_ADDR_LOG) Field Descriptions  | 82  |

| 4-34. | 2-Bit ECC Error Address Log Register (TWO_BIT_ECC_ERR_ADDR_LOG) Field Descriptions  | 83  |

| 4-35. | 1-Bit ECC Error Distribution 2 register (ONE_BIT_ECC_ERR_DIST_2) Field Descriptions | 84  |

| 4-36. | PHY Initialization Register (PIR) Field Descriptions                                | 85  |

| 4-37. | PHY General Configuration Register 0 (PGCR0) Field Descriptions                     | 87  |

| 4-38. | PHY General Configuration Register 1 (PGCR1) Field Descriptions                     | 89  |

| 4-39. | PHY General Configuration Register 2 (PGCR2) Field Descriptions                     | 91  |

| 4-40. | PHY General Status Register 0 (PGSR0) Field Descriptions                            | 92  |

| 4-41. | PHY General Status Register 1 (PGSR1) Field Descriptions                            | 94  |

| 4-42. | PLL Control Register (PLLCR) Field Descriptions                                     | 95  |

| 4-43. | PHY Timing Register 0 (PTR0) Field Descriptions                                     | 96  |

| 4-44. | PHY Timing Register 1 (PTR1) Field Descriptions                                     | 97  |

| 4-45. | PHY Timing Register 2 (PTR2) Field Descriptions                                     | 98  |

| 4-46. | PHY Timing Register 3 (PTR3) Field Descriptions                                     | 99  |

| 4-47. | PHY Timing Register 4 (PTR4) Field Descriptions                                     | 100 |

| 4-48. | AC I/O Configuration Register (ACIOCR) Field Descriptions                           | 101 |

| 4-49. | DATX8 Common Configuration Register (DXCCR) Field Descriptions                      | 102 |

| 4-50. | DRAM Configuration Register (DCR) Field Descriptions                                | 104 |

| 4-51. | DRAM Timing Parameters Register 0 (DTPR0) Field Descriptions                        | 105 |

| 4-52. | DRAM Timing Parameters Register 1 (DTPR1) Field Descriptions                        | 106 |

| 4-53. | DRAM Timing Parameters Register 2 (DTPR2) Field Descriptions                        | 107 |

| 4-54. | Mode Register 0 (MR0) Field Descriptions                                            |     |

| 4-55. | Mode Register 1 (MR1) Field Descriptions                                            | 110 |

| 4-56. | 5 ( )                                                                               | 112 |

| 4-57. | Mode Register 3 (MR3) Field Descriptions                                            |     |

| 4-58. | ODT Configuration Register (ODTCR) Field Descriptions                               | 114 |

| 4-59. | Data Training Configuration Register (DTCR) Field Descriptions                      |     |

| 4-60. | Impedance Control Register 0 (ZQnCR0) Field Descriptions                            | 116 |

| 4-61. | Impedance Control Register 1 (ZQnCR1) Field Descriptions                            |     |

| 4-62. | Impedance Status Register 0 (ZQnSR0) Field Descriptions                             |     |

| 4-63. | Impedance Status Register 1 (ZQnSR1) Field Descriptions                             | 119 |

| 4-64. | DATX8 General Configuration Register (DXnGCR) Field Descriptions                    | 120 |

| 4-65. | DATX8 General Status Register 0 (DXnGSR0) Field Descriptions                        | 122 |

| 4-66. | DATX8 General Status Register 2 (DXnGSR2) Field Descriptions                        |     |

| 4-67. | DATX8 Local Calibrated Delay Line Register 0 (DXnLCDLR0) Field Descriptions         |     |

| 4-68. | DATX8 Local Calibrated Delay Line Register 1 (DXnLCDLR1) Field Descriptions         |     |

| 4-69. | DATX8 Local Calibrated Delay Line Register 2 (DXnLCDLR2) Field Descriptions         |     |

| 4-70. | DATX8 Master Delay Line Register (DXnMDLR) Field Descriptions                       |     |

| 4-71. | DATX8 General Timing Register (DXnGTR) Field Descriptions                           | 128 |

# Preface

# **About This Manual**

The DDR3 memory controller is used to interface with JESD79-3C standard compliant SDRAM devices. Memory types such as DDR1 SDRAM, DDR2 SDRAM, SDR SDRAM, SBSRAM, and asynchronous memories are not supported. The DDR3 memory controller SDRAM can be used for program and data storage.

### **Notational Conventions**

This document uses the following conventions:

- Commands and keywords are in **boldface** font.

- Arguments for which you supply values are in *italic* font.

- Terminal sessions and information the system displays are in screen font.

- Information you must enter is in **boldface screen font**.

- Elements in square brackets ([]) are optional.

Notes use the following conventions:

**NOTE:** Means reader take note. Notes contain helpful suggestions or references to material not covered in the publication.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### CAUTION

Indicates the possibility of service interruption if precautions are not taken.

# WARNING

Indicates the possibility of damage to equipment if precautions are not taken.

#### **Related Documentation from Texas Instruments**

| C66x CorePac User Guide                                                 | SPRUGW0 |

|-------------------------------------------------------------------------|---------|

| C66x CPU and Instruction Set Reference Guide                            | SPRUGH7 |

| Enhanced Direct Memory Access 3 (EDMA3) for KeyStone Devices User Guide | SPRUGS5 |

| External Memory Interface (EMIF16) for KeyStone Devices User Guide      | SPRUGZ3 |

| Interrupt Controller (INTC) for KeyStone Devices User Guide             | SPRUGW4 |

All trademarks are the property of their respective owners.

About This Manual

www.ti.com

# Introduction

Page

This document describes the operation of the DDR3 module in the KeyStone II devices. (Refer to the device-specific data manual for exact device applicability.) The DDR3 module is accessible across all the cores and all system masters that are not cores.

#### Topic

| 1.1 | Purpose of the Peripheral                 | 12 |

|-----|-------------------------------------------|----|

| 1.2 | Features                                  | 12 |

| 1.3 | Industry Standard(s) Compliance Statement | 12 |

# **1.1** Purpose of the Peripheral

The DDR3 memory controller is used to interface with JESD79-3E standard compliant SDRAM devices. Memory types such as DDR1 SDRAM, DDR2 SDRAM, SDR SDRAM, SBSRAM, and asynchronous memories are not supported. The DDR3 memory controller SDRAM can be used for program and data storage. The KeyStone II devices have one (DDR3A) or two (DDR3A and DDR3B) instances depending on the device variant. See the KeyStone II Data Manual. DDR3A is accessed via the MSMC module whereas DDR3B is connected directly to the TeraNet.

# 1.2 Features

The DDR3 controller supports the following features:

- Supports JEDEC standard JESD79-3E DDR3 compliant devices

- 33-bit address for 8 GB of address space

- 16/32/64-bit data bus width support

- CAS latencies: 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15 and 16

- 1, 2, 4, and 8 internal banks

- Burst Length: 8

- Burst Type: sequential

- 8GB address space available over one or two chip selects

- Page sizes: 256, 512, 1024, and 2048-word

- SDRAM auto initialization from reset or configuration change

- Self-refresh mode

- Prioritized refresh scheduling

- Programmable SDRAM refresh rate and backlog counter

- Programmable SDRAM timing parameters

- Big and little endian modes

- ECC on SDRAM data bus (read-modify-write (RMW) ECC to support sub quanta accesses to ECC space (see the section on ECC for applicable device))

- 8-bit ECC per 64-bit data quanta without additional cycle latency

- Two latency classes supported

- UDIMM Address mirroring is supported

- RDIMM is not supported

# 1.3 Industry Standard(s) Compliance Statement

The DDR3 controller is compliant with the JESD79-3E DDR3 SDRAM standard.

# **Peripheral Architecture**

The DDR3 controller interfaces with most standard DDR3 SDRAM devices. It supports self-refresh mode and prioritized refresh. In addition, it provides flexibility through programmable parameters such as the refresh rate, CAS latency, and many SDRAM timing parameters. The following sections describe the architecture of the DDR3 controller as well as how to interface and configure it to perform read and write operations to DDR3 SDRAM devices. Examples for interfacing the DDR3 controller to a common DDR3 SDRAM device are shown in Section 3.1.

#### Topic

#### Page

| 2.1  | Clock Interface                  | 15        |

|------|----------------------------------|-----------|

| 2.2  | SDRAM Memory Map                 | 15        |

| 2.3  | Signal Descriptions              | 15        |

| 2.4  | Protocol Descriptions            | 16        |

| 2.5  | Address Mapping                  | 20        |

| 2.6  | DDR3 Memory Controller Interface | 23        |

| 2.7  | Refresh Scheduling               | <b>26</b> |

| 2.8  | Self-Refresh Mode                | <b>26</b> |

| 2.9  | Reset Considerations             | 27        |

| 2.10 | Turnaround Time                  | <b>28</b> |

| 2.11 | DDR3 SDRAM Memory Initialization | <b>28</b> |

| 2.12 | Leveling                         | 30        |

| 2.13 | Interrupt Support                | 30        |

| 2.14 | EDMA Event Support               | 30        |

| 2.15 | Emulation Considerations         | 30        |

| 2.16 | ECC                              | 30        |

| 2.17 | Data Bus Obfuscation             | 33        |

| 2.18 | Power Management                 | 34        |

| 2.19 | Performance Monitoring           | 34        |

|      |                                  |           |

# 2.1 Clock Interface

There are two clocking schemes in the DDR3 controller - the clocking scheme used to drive the DDR3 controller and the clocking scheme used to drive the DDR3 I/O interface. The DDR3A controller is clocked by DSP/2 clock domain and the DDR3B controller is clocked by DSP/3 clock domain. The I/O interface is driven by the DDR3 A/B memory clock (half the data rate).

### 2.2 SDRAM Memory Map

On KeyStone II devices, both DDR3A and DDR3B have their own controller configuration space and PHY configuration space. For information describing the DDR3 A/B memory map, see the device-specific data manual.

# 2.3 Signal Descriptions

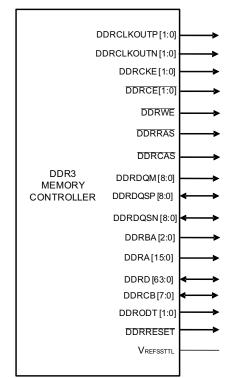

The DDR3 memory controller signals are shown in Figure 2-1 and described in Figure 2-1.

- The maximum data bus is 64-bits wide.

- The address bus is 33-bits wide.

- Two differential output clocks driven by internal clock sources.

- Command signals: Row and column address strobe, write enable strobe, data strobe, and data mask.

- Two chip selects and two clock enable signals.

# Figure 2-1. DDR3 Memory Control Signals

| Table 2-1. DDR3 Memory Controller Signal Descriptions |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin         | Description                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| DDRD [63:0] | Bidirectional data bus. Input for data reads and output for data writes.                                                             |

| DDRCB [7:0] | Bidirectional data bus (check bits) for ECC byte lane. Input for data reads and output for data writes.                              |

| DDRA [15:0] | External address output.                                                                                                             |

| DDRCE0      | Active-low chip enable for memory space CE0. DDRCE0z is used to enable the DDR3 SDRAM memory device during external memory accesses. |

Clock Interface

| Pin                | Description                                                                                                                                |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DDRCE1             | Active-low chip enable for memory space CE1. DDRCE1z is used to enable the DDR3 SDRAM memory device during external memory accesses.       |  |  |  |

| DDRDQM [8:0]       | Active-high output data mask.                                                                                                              |  |  |  |

| DDR3CLKOUTP [1:0]/ | Differential cleak outputs                                                                                                                 |  |  |  |

| DDR3CLKOUTN [1:0]  | Differential clock outputs.                                                                                                                |  |  |  |

| DDRCKE [1:0]       | Clock enable (used for self-refresh mode).                                                                                                 |  |  |  |

| DDRCAS             | Active-low column address strobe.                                                                                                          |  |  |  |

| DDRRAS             | Active-low row address strobe.                                                                                                             |  |  |  |

| DDRWE              | Active-low write enable.                                                                                                                   |  |  |  |

| DDRDQSP [8:0]/     | Differential data stade bilderational simple                                                                                               |  |  |  |

| DDRDQSN [8:0]      | Differential data strobe bidirectional signals.                                                                                            |  |  |  |

| DDRODT [1:0]       | On-die termination signal(s) to external DDR3 SDRAM                                                                                        |  |  |  |

| DDRBA [2:0]        | Bank-address control outputs                                                                                                               |  |  |  |

| VREFSSTTL          | DDR3 Memory Controller reference voltage. This voltage must be supplied externally. For more details, see the device-specific data manual. |  |  |  |

#### Table 2-1. DDR3 Memory Controller Signal Descriptions (continued)

# 2.4 **Protocol Descriptions**

The DDR3 memory controller supports the DDR3 SDRAM commands listed in Table 2-2.

| Command | Function                                                                       |

|---------|--------------------------------------------------------------------------------|

| ACT     | Activates the selected bank and row.                                           |

| PREA    | Precharge all command. Deactivates (precharges) all banks.                     |

| PRE     | Precharge single command. Deactivates (precharges) a single bank.              |

| DES     | Device Deselect.                                                               |

| EMRS    | Extended Mode Register set. Allows altering the contents of the mode register. |

| MRS     | Mode register set. Allows altering the contents of the mode register.          |

| NOP     | No operation.                                                                  |

| PDE     | Power down entry                                                               |

| PDX     | Power down exit                                                                |

| RD      | Inputs the starting column address and begins the read operation.              |

| REF     | Autorefresh cycle                                                              |

| SRE     | Self-refresh entry                                                             |

| SRX     | Self-refresh exit                                                              |

| WR      | Inputs the starting column address and begins the write operation.             |

| ZQCS    | ZQ Calibration short operation                                                 |

| ZQCL    | ZQ Calibration long operation                                                  |

#### Table 2-2. DDR3 SDRAM Commands

Table 2-3 shows the signal truth table for the DDR3 SDRAM commands.

| DDR3<br>SDRAM<br>Signals  | ск              | E              | CS# | RAS#   | CAS#   | WE#   | BA [2:0] | A [15:13] | A12     | A10       | A [9:0],<br>A11 |

|---------------------------|-----------------|----------------|-----|--------|--------|-------|----------|-----------|---------|-----------|-----------------|

| DDR3 Memory<br>controller | DDR<br>Previous | CKE<br>Current |     |        |        |       | DDRBA    | DDRA      | DDRA    | DDRA      | DDRA            |

| signals                   | Cycle           | Cycle          | DCE | DDRRAS | DDRCAS | DDRWE | [2:0]    | [15:13]   | [12]    | [10]      | [9:0],[11]      |

| ACT                       | Н               | Н              | L   | L      | Н      | Н     | BA       |           | Row Add | ress (RA) |                 |

| PREA                      | Н               | Н              | L   | L      | Н      | L     | V        | V         | V       | Н         | V               |

| PRE                       | Н               | Н              | L   | L      | Н      | L     | BA       | V         | V       | L         | V               |

| MRS                       | Н               | Н              | L   | L      | L      | L     | BA       |           | OP      | Code      |                 |

| EMRS <sup>(2)</sup>       | Н               | Н              | L   | L      | L      | L     | BA       | OP Code   |         |           |                 |

| RD (BL8)                  | Н               | Н              | L   | Н      | L      | Н     | BA       | RFU       | V       | L         | CA              |

| WR (BL8)                  | Н               | Н              | L   | Н      | L      | L     | BA       | RFU       | V       | L         | CA              |

| REF                       | Н               | Н              | L   | L      | L      | Н     | V        | V         | V       | V         | V               |

| SRE <sup>(3)</sup>        | Н               | L              | L   | L      | L      | Н     | V        | V         | V       | V         | V               |

| SRX <sup>(3)(4)</sup>     | L               | н              | H   | Х      | Х      | Х     | Х        | Х         | Х       | Х         | Х               |

|                           | L               | п              | L   | Н      | Н      | Н     | V        | Х         | V       | V         | V               |

| NOP                       | Н               | Н              | L   | Н      | Н      | Н     | V        | V         | V       | V         | V               |

| DES <sup>(5)</sup>        | Н               | Н              | Н   | Х      | Х      | Х     | Х        | Х         | Х       | Х         | Х               |

| PDE <sup>(6)</sup>        |                 |                | L   | Н      | Н      | Н     | V        | V         | V       | V         | V               |

|                           | Н               | L              | Х   | Х      | Х      | Х     | Х        | Х         | Х       | Х         | Х               |

| PDX <sup>(6)</sup>        |                 | Н              | L   | Н      | Н      | Н     | V        | V         | V       | V         | V               |

|                           | L               | п              | Х   | Х      | Х      | Х     | Х        | Х         | Х       | Х         | Х               |

| ZQCL                      | Н               | Н              | L   | Н      | Н      | L     | Х        | Х         | Х       | Н         | Х               |

| ZQCS                      | Н               | Н              | L   | Н      | Н      | L     | Х        | Х         | Х       | L         | Х               |

Table 2-3. Truth Table for DDR3 SDRAM Commands<sup>(1)</sup>

(1) LEGEND: H = Logic High, L = Logic Low, X = Don't Care, RA = Row Address, CA = Column Address, RFU = Reserved for future use, V = Valid

<sup>(2)</sup> For extended mode register set (EMRS) command, bank address (BA) pins select an extended mode register (EMR).

<sup>(3)</sup> ODT function is not available during self-refresh.

<sup>(4)</sup> Self-refresh exit (SRE) is asynchronous.

<sup>(5)</sup> The Deselect (DES) command performs the same function as No Operation (NOP).

<sup>(6)</sup> The Power down mode does not perform any self-refresh operation.

# 2.4.1 Mode Register Set (MRS or EMRS)

DDR3 SDRAM contains mode and extended mode registers that configure the DDR3 memory for operation. These registers control burst type, burst length, CAS latency, DLL enable/disable, etc.

The DDR3 memory controller programs the mode and extended mode registers of the DDR3 memory by issuing MRS and EMRS commands. MRS and EMRS commands can be issued during DDR3 initialization as well as during normal operation as long as the external SDRAM is in idle state. When the MRS or EMRS command is executed, the value on DDRBA [1:0] selects the mode register to be written and the data on DDRA [12:0] is loaded into the register. DDRA [15:13] and DDRBA [2] are reserved and are programmed to 0 during MRS (or EMRS).

Each mode register allows programming of different sets of DDR3 SDRAM parameters. The DDR3 memory controller programs the mode registers in compliance with the JEDEC JESD79-3E spec. For more information about mode registers and how they are programmed, see the JEDEC spec.

Protocol Descriptions

www.ti.com

#### 2.4.2 Refresh Mode

The DDR3 memory controller issues refresh commands (REF) to the DDR3 SDRAM device. REF is automatically preceded by a Precharge-all (PREA) command, ensuring the deactivation of all CE spaces and banks selected.

Following the PREA command, the DDR3 memory controller begins performing refreshes at a rate defined by the refresh rate (REFRESH\_RATE) field in the SDRAM refresh control register (SDRFC). In general, a refresh command needs to be issued to the DDR3 SDRAM regularly every tREFI interval. To allow for efficient operation, refresh commands can be postponed a maximum of 8 times. Also, at any given time a maximum of 16 refresh commands can issued within a 2 xtREFI interval. For more information on refresh command timing, see the JEDEC spec.

# 2.4.3 Activation

The ACTIVE command is used to open (or activate) a row in a specific bank for a subsequent access. DDRBA [2:0] select the bank, and the address provided on DDRA[15:0] selects the row. This row remains active (or open) for accesses until a precharge command is issued to that bank. A PRECHARGE command must be issued before opening a different row in the same bank.

When the DDR3 memory controller issues an ACT command, a delay of tRCD is incurred before a read or write command is issued. Reads or writes to the currently active row and bank of memory can achieve much higher throughput than reads or writes to random areas because every time a new row is accessed, the ACT command must be issued and a delay of tRCD incurred.

# 2.4.4 Deactivation

The precharge command is used to deactivate the open row in a particular bank (PRE) or the open row in all banks (PREA). The bank(s) will be available for a subsequent row activation a specified time (tRP) after the precharge command is issued, except in the case of concurrent auto precharge, where a read or write command to a different bank is allowed as along as it does not interrupt the data transfer in the current bank and does not violate any other timing parameters. A PRE command is allowed if there is no open row in that bank (idle state) or if the previously open row is already in the process of precharging. During a PREA command, DDRA [10] is driven high to ensure deactivation of all banks.

# 2.4.5 READ Command

Figure 2-2 shows the DDR3 memory controller performing a read burst from DDR3 SDRAM. The READ command initiates a burst read operation to an active row. The column address is driven on DDRA [15:0], and the bank address is driven on DDRBA [2:0].

The DDR3 memory controller uses a burst length of 8, and has a programmable CAS latency of 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15 or 16. The CAS latency is five cycles in Figure 2-2. In this figure it has been programmed to CL + 1. Because the default burst size is 8, the DDR3 memory controller returns 8 words of data for every read command. Word size is nothing but the DDR3 interface bus width.

If additional accesses are not pending to the DDR3 memory controller, the read burst completes and the unneeded data is disregarded. If additional accesses are pending, based on the arbitration result, the DDR3 memory controller can terminate the read burst and start a new read burst.

#### Figure 2-2. READ Command

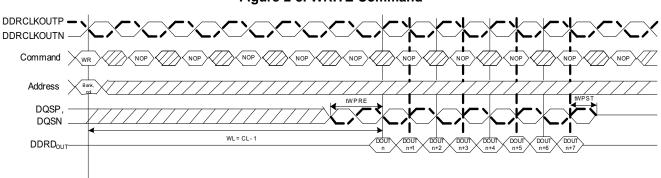

# 2.4.6 Write (WR) Command

Prior to a WRT command, the desired bank and row are activated by the ACT command. Following the WRT command, a write latency is incurred. Write latency is equal to CAS latency minus 1. All writes have a burst length of 8.

Figure 2-3 shows the timing for a write on the DDR3 memory controller. If the transfer request is for less than 8 words, depending on the scheduling result and the pending commands, the DDR3 memory controller can:

- · Mask out the additional data using DDRDQM outputs

- · Terminate the write burst and start a new write burst

#### Figure 2-3. WRITE Command

NOP commands are shown for ease of illustration; other commands may be valid at these times

NOP commands are shown for ease of illustration ; other commands may be valid at these times

### 2.5 Address Mapping

The DDR3 memory controller views external DDR3 SDRAM as one continuous block of memory across the two chip-selects. If smaller devices are used, the memory is seen to roll over. The DDR3 memory controller receives DDR3 memory access requests along with a 33-bit logical address from the rest of the system. The controller uses the logical address to generate a row/page, column, bank address, and chip selects for the DDR3 SDRAM. The number of bank and column address bits used is determined by the IBANK and PAGESIZE fields. The chip selection pins used are determined by the EBANK field (Table 2-4).

| Bit Field | Bit Value | Bit Description                                                                         |

|-----------|-----------|-----------------------------------------------------------------------------------------|

| IBANK     |           | Defines the number of internal banks on external DDR3 memory                            |

|           | 0         | 1 bank                                                                                  |

|           | 1h        | 2 banks                                                                                 |

|           | 2h        | 4 banks                                                                                 |

|           | 3h        | 8 banks                                                                                 |

| PAGESIZE  |           | Defines the page size of each page of the external DDR3 memory                          |

|           | 0         | 256 words (requires 8 column address bits)                                              |

|           | 1h        | 512 words (requires 9 column address bits)                                              |

|           | 2h        | 1024 words (requires 10 column address bits)                                            |

|           | 3h        | 2048 words (requires 11 column address bits)                                            |

| EBANK     |           | External chip select setup. Defines whether SDRAM accesses use 1 or 2 chip select lines |

|           | 0         | Use only chip enable 0 for all SDRAM accesses                                           |

|           | 1         | Use chip enables 0 and 1 for SDRAM accesses                                             |

Table 2-4. Bank Configuration Register Fields for Address Mapping

**NOTE:** IBANK should always be programmed to 3h since DDR3 memory devices offer only 8-bank support unlike DDR2 with the option of 4-bank or 8-bank memory devices.

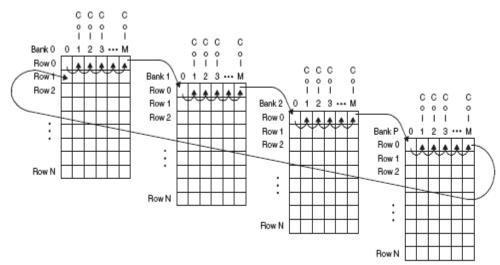

As the source address increments across SDRAM page boundaries, the DDR3 controller moves to the same page in the next bank on the current device (chip select).

After the page has been accessed in all banks of the current device, the same page is accessed in all banks in the next device. This is followed by accessing the next page in the first device and the process continues. To the DDR3 SDRAM, this process looks as shown on Figure 2-5. Thus, the DDR3 controller exploits this traversal across internal banks and chip selects while remaining on the same page to maximize the number of open SDRAM banks within the overall SDRAM space. See Figure 2-5.

Thus 16 banks (eight internal banks across two chip selects) can be kept open at a time, interleaving among all of them.

Address Mapping

www.ti.com

# Table 2-5. Logical Address-to-SDRAM Address Mapping

| Logical Address [32:N]                  |         |                 |                  |                            |                              |                |                        |  |

|-----------------------------------------|---------|-----------------|------------------|----------------------------|------------------------------|----------------|------------------------|--|

| Row A                                   | ddress  | Chip Select     |                  | Bank Address[2:0]          |                              | Column Address |                        |  |

| ROW SIZE                                | nrb     | EBANK           | ncs              | IBANK                      | nbb                          | PAGE SIZE      | ncb                    |  |

| Don't care                              | 16 bits | 0               | 0 bits           | 0                          | 0 bits                       | 0              | 8 bits                 |  |

|                                         |         | 1               | 1 bit            | 1                          | 1 bit                        | 1              | 9 bits                 |  |

|                                         |         |                 |                  | 2                          | 2 bits                       | 2              | 10 bits                |  |

|                                         |         |                 |                  | 3                          | 3 bits                       | 3              | 11 bits                |  |

| Logical address mapping for row address |         | 0               | mapping for chip | Logical addres<br>bank add | ss mapping for<br>fress[1:0] |                | ss mapping for address |  |

| MSB                                     | LSB     | MSB             | LSB              | MSB                        | LSB                          | MSB            | LSB                    |  |

| M3+nrb-1                                | M3+1    | M3=M2+<br>ncs-1 | M2+1             | M2=M1+<br>nbb-1            | M1+1                         | M1=N+<br>ncb-1 | Ν                      |  |

**NOTE:** N=1 for 16-bit SDRAM, N=2 for 32-bit SDRAM and N=3 for 64-bit SDRAM. ROWSIZE is kept for legacy reasons but is not used by the DDR3 controller. nrb = Number of row bits. ncs = Number of chip select bits. nbb = Number of bank select bits determined by bank address [2:0].

Texas Instruments

www.ti.com

|               | Col. M | Col. M-1 | •••   | Col. 4 | Col. 3 | Col. 2 | Col. 1 | Col. 0 |

|---------------|--------|----------|-------|--------|--------|--------|--------|--------|

| Row 0, bank 0 |        |          | • • • |        |        |        |        |        |

| Row 0, bank 1 |        |          | • • • |        |        |        |        |        |

| Row 0, bank 2 |        |          | • • • |        |        |        |        |        |

| •             | •      | •        | • • • | •      | •      | •      | ٠      | •      |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| Row 0, bank P |        |          | • • • |        |        |        |        |        |

| Row 1, bank 0 |        |          | • • • |        |        |        |        |        |

| Row 1, bank 1 |        |          | • • • |        |        |        |        |        |

| Row 1, bank 2 |        |          | • • • |        |        |        |        |        |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| •             | •      | •        | •••   | •      | •      | •      | •      | •      |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| Row 1, bank P |        |          | • • • |        |        |        |        |        |

| •             |        |          | • • • |        |        |        |        |        |

| •             |        |          | • • • |        |        |        |        |        |

| •             |        |          | • • • |        |        |        |        |        |

| Row N, bank 0 |        |          | • • • |        |        |        |        |        |

| Row N, bank 1 |        |          | • • • |        |        |        |        |        |

| Row N, bank 2 |        |          | •••   |        |        |        |        |        |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| •             | •      | •        | • • • | •      | •      | •      | •      | •      |

| Row N, bank P |        |          | •••   |        |        |        |        |        |

### Figure 2-4. Logical Address-to-DDR3 SDRAM Address Map (EBANK=0)

A M is number of columns (as determined by PAGESIZE) minus 1, P is number of banks (as determined by IBANK) minus 1, and N is number of rows (as determined by both PAGESIZE and IBANK) minus 1.

#### Figure 2-5. DDR3 SDRAM Column, Row, and Bank Access (EBANK=0)

A M is number of columns (as determined by PAGESIZE) minus 1, P is number of banks (as determined by IBANK) minus 1, and N is number of rows (as determined by both PAGESIZE and IBANK) minus 1.

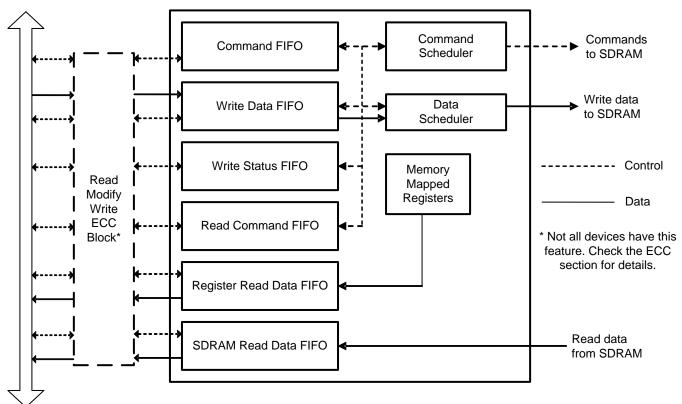

# 2.6 DDR3 Memory Controller Interface

To move data efficiently from on-chip resources to an external DDR3 SDRAM device, the DDR3 memory controller makes use of a Command FIFO, a Write Data FIFO, a Write Status FIFO, a Read Command FIFO, and two Read Data FIFOs and command and data schedulers. Table 2-6 describes the purpose of each FIFO. Figure 2-6 shows the block diagram of the DDR3 memory controller FIFOs. Commands, write data, and read data arrive at the DDR3 memory controller parallel to each other. The same peripheral bus is used to write and read data from external memory as well as internal memory-mapped registers (MMR).

| FIFO               | Description                                                              | Depth             |

|--------------------|--------------------------------------------------------------------------|-------------------|

| Command            | Stores all commands coming from on-chip requestors                       | 16                |

| Write Data         | Stores write data coming from on-chip requestors to memory               | 20 (512-bit wide) |

| Write Status       | Stores the write status information for each write transaction           | 7                 |

| Read Command       | Stores all read transactions that are to be issued to on-chip requestors | 28                |

| SDRAM Read Data    | Stores read data coming from SDRAM memory to on-chip requestors          | 28 (256-bit wide) |

| Register Read Data | Stores read data coming from MMRs to on-chip requestors                  | 2 (256-bit wide)  |

Table 2-6. DDR3 Memory Controller FIFO Description

#### Figure 2-6. DDR3 Memory Controller FIFO Block Diagram

#### 2.6.1 Arbitration

The DDR3 memory controller performs command reordering and scheduling in an attempt to achieve efficient transfers with maximum throughput. The goal is to maximize the utilization of the data, address, and command buses while hiding the overhead of opening and closing DDR3 SDRAM rows. Command reordering takes place within the command FIFO.

The DDR3 memory controller examines all the commands stored in the command FIFO to schedule commands to the external memory. For each master, the DDR3 memory controller reorders the commands based on the following rules:

- The DDR3 controller will advance a read command before an older write command from the same master if the read is to a different block address (2048 bytes) and the read priority is equal to or greater than the write priority.

- The DDR3 controller will block a read command, regardless of the master or priority if that read command is to the same block address (2048 bytes) as an older write command.

Thus, one pending read or write for a master might exist.

- Among all pending reads, the DDR3 controller selects all reads that have their corresponding SDRAM banks already open.

- Among all pending writes, the DDR3 controller selects all writes that have their corresponding SDRAM banks already open.

As a result of the above reordering, several pending reads and writes may exist that have their corresponding banks open. The highest priority read is selected from pending reads, and the highest priority write from pending writes. If two or more commands have the highest priority, the oldest command is selected. As a result, there might exist a final read and a final write command. Either the read or the write command will be selected depending on the value programmed in the Section 4.27.

The DDR3 controller supports interleaving of commands for maximum efficiency. In other words, the controller will partially execute one command and switch to executing another higher priority command before finishing the first command.

Apart from reads and writes the DDR3 controller also needs to open and close SDRAM banks, and maintain the refresh counts for an SDRAM. The priority of SDRAM commands with respect to refresh levels are as follows:

- 1. (Highest priority) SDRAM refresh request due to Refresh Must level of refresh urgency reached.

- 2. Read request without a higher priority write (from the reordering algorithm above)

- 3. Write request.

- 4. SDRAM Activate commands.

- 5. SDRAM Deactivate commands.

- 6. SDRAM Power-Down request.

- 7. SDRAM refresh request due to Refresh May or Release level of refresh urgency reached.

- 8. (Lowest priority) SDRAM self-refresh request.

#### 2.6.2 Command Starvation

While running the scheduling algorithm described in Section 2.6.1, the DDR3 memory controller is subject to the following:

- 1. A continuous stream of high priority commands can block lower priority commands.

- 2. A continuous stream of SDRAM commands to a row in an open bank can block commands to another row in the same bank.

To avoid a continuous blocking effect, the priority of the oldest command is momentarily raised over all other commands when the latency counter for the oldest command expires. The latency counter for the oldest command (PR\_OLD\_COUNT) is configurable in the Latency Configuration Register. In addition to this, the order of command accesses can also be tailored by grouping commands into two categories or "classes" and assigning different latency expiration counters to each category. See Section 2.6.4 for more information.

On top of the above scheduling, the highest priority condition is a removal of hard or soft reset. If this occurs, the DDR3 controller abandons whatever it is currently doing and commences its startup sequence. In this case, commands and data stored in the FIFOs are lost. The startup sequence also commences whenever the SDRAM Config register is written and INITREF\_DIS field in SDRAM Refresh Control register (SDRFC) is set to 0. In this case, commands and data stored in the FIFOs are not lost. The DDR3 controller will ensure that in-flight read or write transactions to the SDRAM are complete before starting the initialization sequence.

# 2.6.3 Possible Race Condition

A race condition may exist when certain masters write data to the DDR3 memory controller. For example, if master A passes a software message via a buffer in DDR3 memory and does not wait for indication that the write completes, when master B attempts to read the software message it may read stale data and therefore receive an incorrect message. In order to confirm that a write from master A has landed before a read from master B is performed, master A must wait for the write to complete before indicating to master B that the data is ready to be read. For example, an EDMA transfer controller should wait for the transfer completion event to occur before signaling a CorePac to read the message from DDR3.

If master A does not wait for indication that a write is complete, it must perform the following workaround:

- 1. Perform the required write.

- 2. Perform a dummy write to the DDR3 memory controller module ID and revision register.

- 3. Perform a dummy read to the DDR3 memory controller module ID and revision register.

- 4. Indicate to master B that the data is ready to be read after completion of the read in step 3. The completion of the read in step 3 ensures that the previous write was done.

# 2.6.4 Class of Service

The commands in the Command FIFO can be mapped to two classes of service: 1 and 2. The mapping of commands to a particular class of service can be done based on the priority or the master ID. The mapping based on priority can be done by setting the appropriate values in the Priority to Class of Service Mapping register. The mapping based on master ID can be done by setting the appropriate values of master ID and the masks in the Master ID to Class of Service Mapping registers.

There are three master ID and mask values that can be set for each class of service. In conjunction with the masks, each class of service can have a maximum of 144 master IDs mapped to it. For example, a master ID value of 0xFF along with a mask value of 0x3 will map all master IDs from 0xF8 to 0xFF to that particular class of service. By default all commands will be mapped to class of service 2.

Each class of service has an associated latency counter. The value of this counter can be set in the Latency Configuration register. When the latency counter for a command expires, i.e., reaches the value programmed for the class of service that the command belongs to, that command will be the one that is executed next. If there is more that one command that has expired latency counters, the command with the highest priority will be executed first. One exception to this rule is as follows: if any of the commands with the expired latency counters is also the oldest command in the queue, that command will be executed first irrespective of priority. This is done to prevent a continuous block effect as described in Section 2.6.1.

DDR3 Memory Controller Interface

#### 2.7 Refresh Scheduling

The DDR3 controller uses two counters to schedule AUTO REFRESH commands:

- · a 13-bit decrementing refresh interval counter

- a four-bit refresh backlog counter

The interval counter is loaded with the REFRESH\_RATE field value at reset. The interval counter decrements by one each cycle until it reaches zero at which point it reloads from REFRESH\_RATE and restarts decrementing. The counter also reloads and restarts decrementing whenever the REFRESH RATE field is updated.

The refresh backlog counter records the number of AUTO REFRESH commands that are currently outstanding. The backlog counter increments by one each time the interval counter reloads (unless it has reached its maximum value of 15). The backlog counter decrements by one each time the DDR3 controller issues an AUTO REFRESH command (unless it is already at zero). Following a refresh command, the DDR3 memory controller waits T\_RFC cycles, defined in the SDRAM timing 3 register (SDTIM1), before rechecking the refresh urgency level.

For the range of values that the backlog counter can take, there are three levels of urgency with which the DDR3 controller should perform an auto refresh cycle (in which it issues AUTO REFRESH commands), as follows:

- Refresh May level is reached whenever the backlog count is greater than 0, to indicate that there is a refresh backlog, so if the DDR3 controller is not busy and none of the SDRAM banks are open, it should perform an auto refresh cycle.

- Refresh Release level is reached whenever the backlog count is greater than 4, to indicate that the

refresh backlog is getting high, so if the DDR3 controller is not busy it should perform an auto refresh

cycle even if any banks are open.

- Refresh Must level is reached whenever the backlog count is greater than 7, to indicate that the refresh backlog is getting excessive and the DDR3 controller should perform an auto refresh cycle before servicing any new memory access requests.

The DDR3 controller starts servicing new memory accesses after Refresh Release level is cleared. If any of the commands in the Command FIFO have class-of-service latency counters that are expired, the DDR3 controller will not wait for Refresh Release level to be cleared but will only perform one refresh command and exit the refresh state.

The refresh counters do not operate when SDRAM has been put into self-refresh mode. Also, the refresh counters start tracking the missed refreshes only after initialization is complete.

#### 2.8 Self-Refresh Mode

The DDR3 memory controller supports self-refresh mode for low power. The controller maintains DDRCKE low to maintain the self-refresh state. In self-refresh, the memory maintains valid data while consuming a minimal amount of power.

Self-refresh mode is set by programming the LP\_MODE in the Power Management Control register (PMCTL) to 2. The controller automatically puts the SDRAM into self-refresh after the controller is idle for SR\_TIM DDR3CLKOUT cycles. (See Section 4.9 for more information.)

The memory is brought out of self-refresh under any of the following conditions:

- If the LP\_MODE field is set not equal to 2

- A memory access is requested

- SR\_TIM bit in PMCTL is cleared

In a situation where memory accesses and a self-refresh command are sent to the DDR3 memory controller, the controller always prioritizes the memory access. Thus, if a reset is triggered when memory accesses and a self-refresh command are queued in the controller, it is likely that self-refresh will not be entered.

The user must ensure that all memory accesses have been completed, and verify that self-refresh is set in the STATUS register before initiating a reset.

**NOTE:** The DDR3 memory controller completes all pending memory accesses and refreshes before it puts SDRAM into self-refresh. If a request for a memory access is received, the DDR3 memory controller services the memory access request then returns to the self-refresh state upon completion.

# 2.8.1 Extended Temperature Range

The normal operating temperature range for DDR3 SDRAMs is typically 0 to 85°C. When operating in selfrefresh mode within the extended temperature range (85°C to 95°C), the memory device must be refreshed at 2x the normal refresh rate. For this purpose, either the auto self-refresh (ASR) or self-refresh temperature (SRT) feature should be used. Under normal operating conditions, both ASR and SRT should be disabled (equal to 0). When ASR is enabled, the internal refresh rate of the SDRAM automatically switches to 2x the refresh rate when the operating case temperature Tc is greater than 85°C when in Selfrefresh mode. When SRT is enabled, the internal refresh rate of the SDRAM is forced to 2x the refresh rate regardless of Tc. Both SRT and ASR cannot be enabled at the same time. One must be disabled if the other is enabled.

**NOTE:** ASR and SRT are used only in self-refresh mode (LP\_MODE=0x2). When operating in extended temperature range with LP\_MODE = 0x0 (not in self-refresh), it is up to the user to program the manual refresh rate to 2x the normal refresh rate for proper operation. If it is guaranteed that Tc will exceed 85°C, it is recommended that SRT=1 to force the refresh rate to 2x regardless of operating temperature.

# 2.9 Reset Considerations

The DDR3 memory controller can be reset through a hard reset or a soft reset. A hard reset resets the state machine, the FIFOs, and the internal registers. A soft reset only resets the state machine and the FIFOs. A soft reset does not reset the internal registers except for the interrupt registers. Register accesses cannot be performed while either reset is asserted.

The DDR3 memory controller hard and soft reset are derived from device-level resets. Table 2-7 shows the relationship between the device-level resets and the DDR3 memory controller resets. For more information on the device-level resets, see the device-specific data manual.

| DDR3 Memory Controller | Reset Effect                                                  | Initiated by                                                                                        |

|------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Hard reset             | Resets control logic and all DDR3 memory controller registers | <ul> <li>Please refer to the reset controller<br/>description in your device data manual</li> </ul> |

| Soft reset             | Resets control logic and interrupt registers                  | <ul> <li>Please refer to the reset controller<br/>description in your device data manual</li> </ul> |

| Table 2-7. Device and DDR3 Memory | v Controller Reset Relationshin |

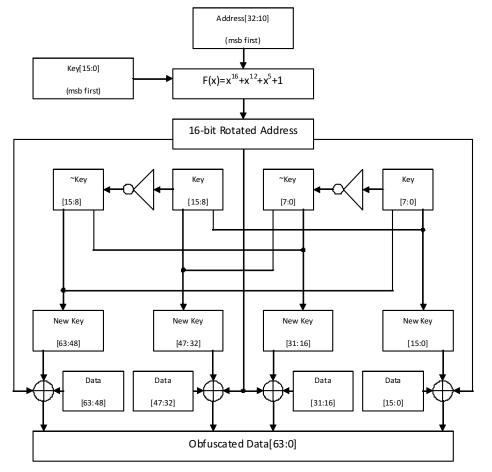

|-----------------------------------|---------------------------------|