设计指南: TIDM-02002

# 针对 HEV/EV 车载充电器的双向 CLLLC 谐振双有源电桥 (DAB) 参考设计

# TEXAS INSTRUMENTS

### 说明

具有双向电源流功能和软开关特性的 CLLLC 谐振 DAB 是混合动力电动汽车/电动汽车 (HEV/EV) 车载充电器和能源存储应用的一种理想 候选方案。此设计演示了在闭合电压和闭合电流环路模式中使用 C2000™MCU 控制此电源拓扑。采用此设计的硬件和软件可帮助您缩短产品上市时间。

### 资源

| TIDM-02002                 | 设计文件夹 |

|----------------------------|-------|

| TMS320F280049              | 产品文件夹 |

| UCC21530-Q1                | 产品文件夹 |

| AMC1311-Q1                 | 产品文件夹 |

| AMC1302-Q1                 | 产品文件夹 |

| LMV116                     | 产品文件夹 |

| OPA320                     | 产品文件夹 |

| C2000WARE-DIGITAL-POWERSDK | 软件文件夹 |

| PMP21553                   | 设计文件夹 |

| PMP21561                   | 设计文件夹 |

| PMP21495                   | 设计文件夹 |

| TMDSCNCD280049C            | 工具文件夹 |

|                            |       |

Search Our E2E™ support forums

### 特性

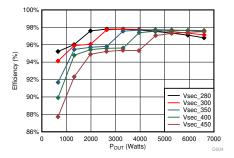

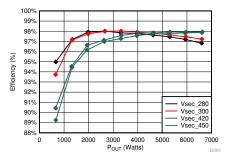

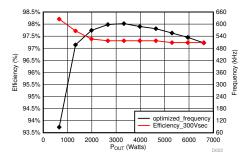

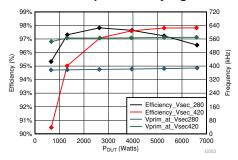

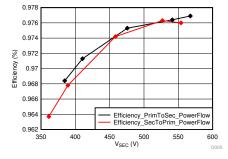

- Vprim: 380-600V 直流; Vsec: 280-450V 直流

- 功率最大值: 6.6kW, 峰值效率为 98%

- 具有 500kHz 额定 PWM 开关(范围: 300kHz-700kHz)的 CLLLC 谐振回路可以实现更高的功率 密度

- 软开关在初级侧使用零电压开关 (ZVS); 在次级侧使 用零电流开关 (ZCS) 和 ZVS,可实现更高的效率

- 使用 Rogowski 线圈传感器实现有源同步整流方案, 可实现更高的效率

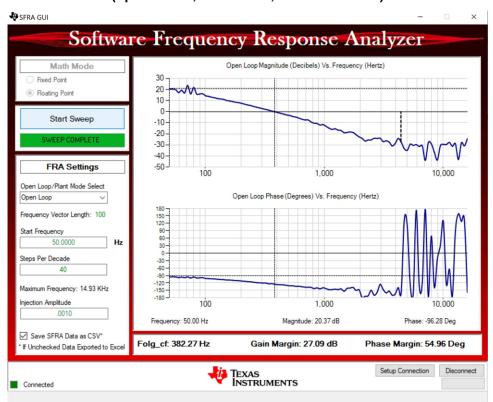

- 软件频率响应分析器 (SFRA) 和补偿设计器便于控制 环路调优

- 控制律加速器 (CLA) 为 TMS320F28004x 器件提供 软件支持,可以实现通过单一 C2000 MCU 控制交 流/直流和直流/直流的集成式 OBC 设计。

### 应用

- 用于 EV 的车载充电器

- 非车载充电器

- 电网储能

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

### 1 System Description

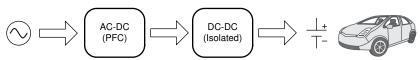

On-board chargers (OBCs) are an essential part of Electric Vehicles (EVs) and Hybrid Electric Vehicles (HEV). An OBC typically consists of an AC-DC [power factor correction (PFC) rectifier stage] and an isolated DC-DC converter, as shown in 🖺 1. C2000 MCUs are designed to implement advanced digital power control that automotive applications demand; for more information, see C2000 Digital Power and C2000 EV.

### 图 1. Typical OBC Architecture

The ability to charge the battery fully overnight is highly desired for most EV Level 1 and Level 2 chargers. With battery capacity increasing, the OBCs need to be designed for even higher power. With the increasing power capacity of the OBC, specifications such as power density and efficiency are even more important, due to limited space and cooling capacity in the car.

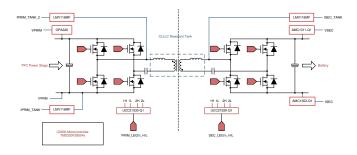

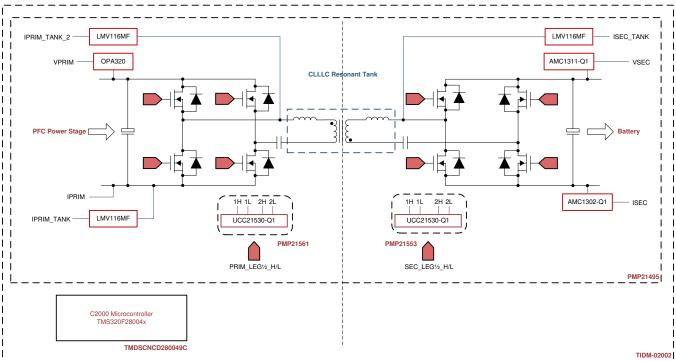

The CLLLC (Capacitor-Inductor-Inductor-Inductor-Capacitor)—with its symmetric tank, soft switching characteristics, and ability to switch at higher frequencies—is a good choice for these applications. In this design, control and implementation of a CLLLC topology, as shown in  $\[mathbb{g}\]$  2, is illustrated.

# PRIM\_TANK\_2 VPRIM IPRIM\_TANK\_2 VSEC CLLLC Resonant Tank USEC\_TANK VSEC VSEC IH 1L 2H 2L IPRIM\_TANK PRIM\_LEG/½\_H/L SEC\_LEG/½\_H/L

图 2. CLLLC Topology for Isolated DC-DC Converter

The nomenclature for \bigseparty 2 is as follows:

VPRIM Primary side voltage (typically comes from a PFC converter)

IPRIM Return current of the primary side, can be used for protection

and monitoring.

Tank current on the primary side, two methods to sense using shunt current sense and other is rogowski's coil. Only one is IPRIM\_TANK, IPRIM\_TANK\_2 needed, used to implement synchronous rectification in the

reverse direction i.e. secondary to primary. Also used for

protection.

VSEC Secondary side voltage (typically, a battery)

ISEC Return current of the secondary side, used to implement the

battery current control loop.

2

www.ti.com.cn System Description

Tank current on the secondary side, used to implement the SEC\_TANK synchronous rectification for the foward direction power flow i.e.

primary to secondary.

PRIM\_LEG1/2\_H/L PWMs for the primary side full bridge SEC\_LEG1/2\_H/L PWMs for the secondary side full bridge

System Description www.ti.com.cn

### 1.1 Key System Specifications

The CLLLC reference design power specifications are listed in 表 1.

### 表 1. Key System Specifications

| PARAMETER               | SPECIFICATIONS                                                     |

|-------------------------|--------------------------------------------------------------------|

| Prim Voltage (Vprim)    | 380 V-600 V DC (typically sourced from a PFC stage, max ripple 5%) |

| Sec Voltage (Vsec)      | 280 V-450 V DC (connected to the battery)                          |

| Power Rating            | 6.6 kW Max                                                         |

| Output Current (lout)   | 18 A Max                                                           |

| Efficiency              | Peak 98%                                                           |

| PWM Switching Frequency | 500 kHz Nominal (300 kHz-700 kHz Range)                            |

### **WARNING**

TI intends this design to be operated in a lab environment only and does not consider it to be a finished product for general consumer use. The design is intended to be run at ambient room temprature and is not tested for operation under other ambient tempratures.

There are accessible high voltages present on the board. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled or applied. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property.

### **CAUTION**

Do not leave the design powered when unattended.

www.ti.com.cn System Description

TI considers it the user's responsibility to confirm that the voltages and isolation requirements are identified and understood before energizing the board or simulation. When energized, do not touch the design or components connected to the design.

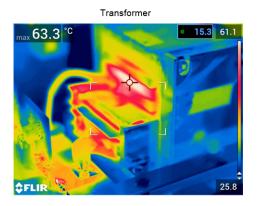

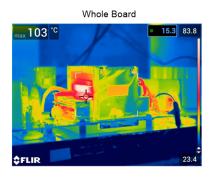

### WARNING

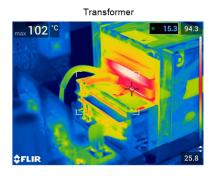

Hot surface! Contact may cause burns. Do not touch!

Some components may reach high temperatures >55°C when the board is powered on. The user must not touch the board at any point during operation or immediately after operating, as high temperatures may be present.

### 2 System Overview

### 2.1 Block Diagram

§ 3 shows the block diagram of the CLLLC topology.

### 图 3. TIDM-02002 Block Diagram -----

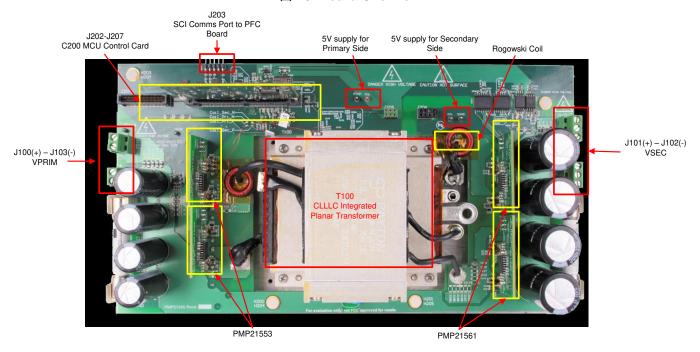

This reference design uses the following EVMs and PMP designs to achieve operation as documented in this guide:

- 1. CLLLC Base Board: PMP21495

- 2. Safety isolated primary SiC MOSFET driver reference design: PMP21553

- Safety isolated secondary SiC MOSFET driver reference design: PMP21561

- 4. F280049C controlCARD Evaluation Module: TMDSCNCD280049C

The following sections discuss details of the hardware, software and system design.

### 2.2 Design Considerations and System Design Theory

LLC converters are widely popular due to their ability to achieve ZVS at the primary side, and ZCS on the secondary side. However, LLC converters suffer when operating away from the resonant frequency point, as the resonant tank current increases and switching losses rise along with the loss of ZCS. However, with the use of silicon carbide (SiC) for higher power chargers, SiC power devices are typically rated for 900 V+", which allows the output voltage of the PFC converter to be varied in a wide range. This can then be used to operate the LLC at resonance or close-to-resonance frequency, which can eliminate these drawbacks of LLC converters when operating under wide output voltage range.

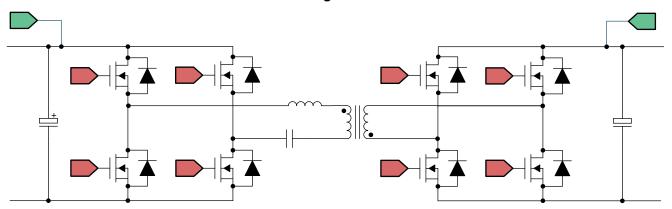

A typical LLC Series Resonant Converter (SRC) is shown in

4. The primary side of this converter is half bridge; thus, the transformer utilization from a Volt-sec perspective is half. In addition, the current rating for the switches is twice of what is needed, compared to when a full-bridge structure is used.

### 图 4. LLC Half-Bridge SRC

Although half-bridge LLC SRCs are attractive at lower power for cost reasons, for high-power and high-density applications, a full-bridge LLC SRC is desired for the following reasons:

- 1. A full-bridge LLC converter better utilizes the magnetic core of the transformer on both the secondary side and primary side; therefore, it is able to offer better power density.

- 2. A full-bridge LLC converter reduces current rating; and therefore, reduces the cost of copper in wires. It also enables higher power (compared to half-bridge SRCs) to be achieved with the same copper wires.

图 5. Full-Bridge LLC Converter

A full-bridge LLC converter, as shown in 🛭 5, falls under the broad category of Dual Active Bridge (DAB) converters. Under DAB converters, the converter can be classified on the basis of model or operation:

- 1. A phase-shifted DAB converter is one of the most popular converters historically.

- 2. Resonant DAB converters have different variants on resonant tanks (LC, LLC, CLLC, CLLC, and so forth).

Resonant DAB converters are of interest because high efficiency, high power, and high density are achievable with such converters. CLLLC, with its symmetric tank, is capable of bidirectional operation. The problem with using an LLC structure for bidirectional use is that the switching frequency, when operating in the reverse power flow mode, is governed by the transformer winding capacitance and the leakage inductance. This offers little or no control on the gain of the power stage and the switching frequency. Therefore, the CLLLC type of structure is preferred as it offers much better control on the switching frequency and an additional degree of freedom on the gain.

One of the biggest challenges with resonant converters is the operation across a wide input/output voltage range. This is particularly challenging with battery-charging type applications where the battery voltage varies widely from 280 V to 450 V. Techniques in literature have been presented to mitigate this with a variable DC link voltage from the PFC. This design relies on the ability to regulate the PFC voltage in a 380 V–6000 V range; a resonant tank is designed to cover that range of voltages.

### 2.2.1 Tank Design

In this section, the tank parameter selection for the CLLLC is discussed based on the voltage gain desired, soft switching characteristics, and an appropriate power profile is selected for the charger based on CLLLC.

For additional calculations and information, refer to the following files located inside the software install package at C2000Ware\_DigitalPower\_SDK\_<ver>>/solution/tidm\_02002/hardware/

- 1. CLLLC calculations.xlsx (Excel file)

- 2. CLLLC\_tankSimulation.m (MATLAB file)

### 2.2.1.1 Voltage Gain

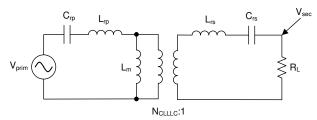

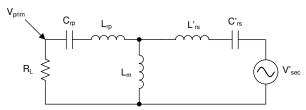

To understand tank design, first the gains for both battery-charging mode and reverse-power-flow mode must be analyzed with First Harmonic Analysis (FHA) using first harmonic approximation. The simplified diagram of the resonant tank is given in [8] 6.

### 图 6. FHA Model for CLLLC Resonant Tank During Battery Charging Mode (BCM)

The nomenclature for \( \bigsize 6 \) is as follows:

| Voltage input at primary side   |  |

|---------------------------------|--|

| Primary side resonant inductor  |  |

| Primary side resonant capacitor |  |

| Turns ratio of the transformer  |  |

|                                 |  |

L<sub>m</sub> Magnetizing inductor

$\begin{array}{lll} V_{\text{sec}} & & \text{Voltage output at secondary side} \\ L_{\text{rs}} & & \text{Secondary side resonant inductor} \\ C_{\text{rs}} & & \text{Secondary side resonant capacitor} \end{array}$

R<sub>L</sub> Effective load seen with FHA on the secondary output

Note here the effective  $R_L$  is accounted for as  $R_L = \left(\frac{8}{\pi^2}\right) R_{L\_dc}$  where  $R_{L\_dc}$  is the DC resistive load at the output.

Referring to secondary side quantities on the primary side,

L<sub>rs</sub>' is equal to L<sub>rs</sub> \* N<sub>CLLLC</sub> \* N<sub>CLLLC</sub>

- $C_{rs}'$  is equal to  $C_{rs} / (N_{CILIC} * N_{CILIC})$

- R<sub>L</sub>' is equal to R<sub>L</sub> \* (N<sub>CLLLC</sub> \* N<sub>CLLLC</sub>)

- $V_{rs}$ ' is equal to  $V_{rs}$  \*  $N_{CLLLC}$

### 图 7. FHA CLLLC With Quantities Referred to Primary Side in BCM

Using KCL and KVL, the gain equation can be written as 公式 1.

$$\frac{V_{sec}}{V_{prim}} = \frac{\left[Z_{m} \parallel \left(Z_{rs}^{'} + R_{L}^{'}\right)\right] R_{L}^{'}}{\left(Z_{rp} + \left[Z_{m} \parallel \left(Z_{rs}^{'} + R_{L}^{'}\right)\right]\right) \left(Z_{rs}^{'} + R_{L}^{'}\right) N_{CLLLC}}$$

(1)

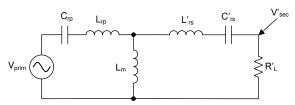

Similarly, for the reverse power flow, the circuit can be simplified as shown in 8, and the gain can be written as 2.

$$\frac{V_{prim}}{V_{sec}} = \frac{N_{CLLLC} \left[ Z_m \mid\mid \left( Z_{rp} + R_L \right) \right] R_L}{\left( Z_{rs}' + \left[ Z_m \mid\mid \left( Z_{rp} + R_L \right) \right] \right) \left( Z_{rp} + R_L \right)}$$

(2)

### 图 8. FHA Model for Gain Calculation in RCM

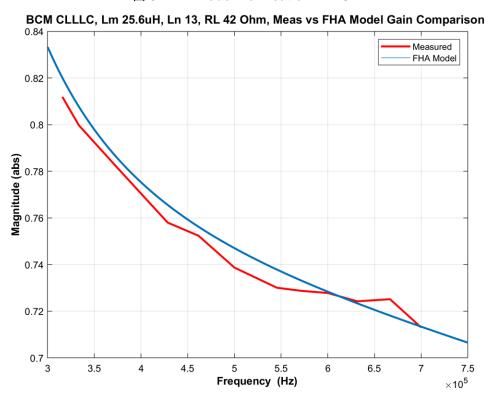

公式 1 and 公式 2 are used in the following section to study the voltage gain based on the parameters selected for the design. The FHA model described above is verified by the measurement on the designed CLLLC, as shown in 图 9.

图 9. FHA Model Verification in BCM

### 2.2.1.2 Transformer Gain Ratio Design (N<sub>CLLLC</sub>)

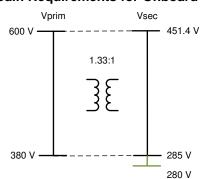

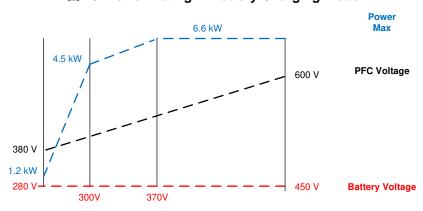

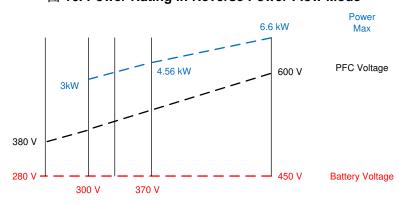

The first part in tank design is to identify the voltage gain desired for the application. As the design is intended to work with a variable PFC bus voltage (380 V−600 V) to generate voltage from 280 V−450 V, a turns ratio of 1.33 is selected, as shown in 🖺 10. This enables operation at resonance for the CLLLC for a wide range of operations.

图 10. Gain Requirements for Onboard Charger

### 2.2.1.3 Magnetizing Inductance Selection $(L_m)$

To ensure ZVS operation of the primary side FETs, we need to make sure the energy stored in the resonant tank is greater than the energy stored in the FET output capacitors. We can use  $\triangle \vec{\pi}$  3 to determine the needed L<sub>m</sub> for full-bridge LLC SRCs.

$$L_{m} \le \frac{Tt_{dead}}{16 * C_{oss}} \tag{3}$$

where the intended switching frequency for the converter is 500 kHz, hence T =  $1/(500 * 10^3)$ , and based on the power device (that is, the SiC MOSFET). Selected parameters such as  $t_{dead}$  and  $C_{oss}$  can also be identified from the power device data sheet. Typically, the effective  $C_{oss}$  must be calculated using curve fitting (see the  $C_{oss}$  effective sheet in CLLLC\_calculations.xlsx). On this design, based on the design parameters discussed,  $L_m$  must be less than 48  $\mu$ H. In addition to what is accounted for in the above calculation, there is interwinding capacitance in a real transformer that needs to be discharged by the resonant tank current. Therefore, using simulation, a value of 25  $\mu$ H was selected to ensure ZVS across the operating range of the converter; this value is used in the subsequent selection processes.

### 2.2.1.4 Resonant Inductor and Capacitor Selection ( $L_{rp}$ and $C_{rp}$ )

While selecting  $L_{ro}$ , the ratio of  $L_{m}$  to  $L_{ro}$  is widely used as a design parameter,

$$L_{n} = \frac{L_{m}}{L_{rp}} \tag{4}$$

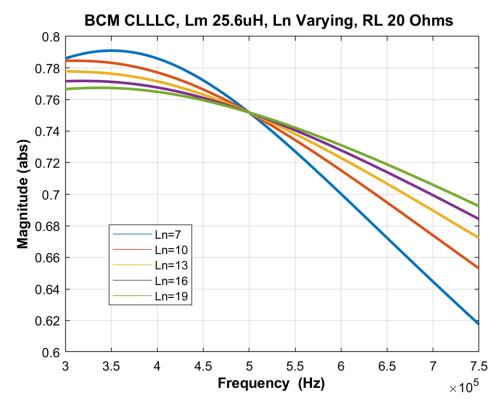

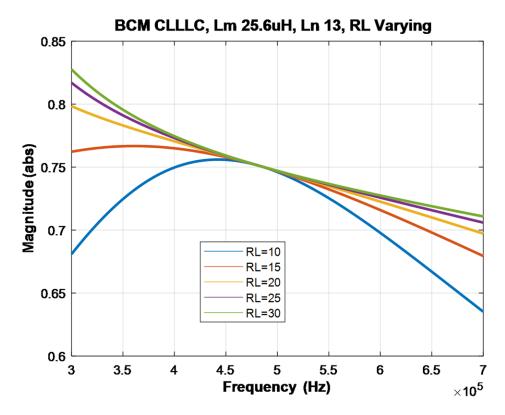

The  $L_n$  value is selected such that it ensures the voltage gain in the resonant tank is enough across the operating range of the converter. In this design, as the input voltage comes from a PFC stage and will have a 10% ripple, a gain variation of at least 10% is needed. With this criteria in mind and the fact that  $L_n$  should be kept higher to reduce the inductor value, and hence the losses,  $L_n$  equal to 13 is selected for this design, based on the plot of the FHA with  $L_n$  varying (see  $\mathbb R$  11).

### 图 11. CLLLC Tank Gain Variation With L<sub>n</sub> Varying

Now that the selection of  $L_n$  is made,  $L_p$  can be calculated using  $\triangle \mathbb{R}$  4.  $L_p$  and  $C_p$  determine the series resonant frequency of the converter and they are related by  $\triangle \mathbb{R}$  5.

$$f_{res} = \frac{1}{2\pi\sqrt{L_{rp}C_{rp}}} \tag{5}$$

公式 5 can then be used to calculate the  $C_{rp}$  needed on the design. However, due to component availability, the next closest value of  $C_{rp}$  is used on the design. With these component values, the BCM gain is shown in 图 12.

##

In  $\boxtimes$  12, as the load increases (that is,  $R_{L\_dc}$  goes lower), the gain curve becomes non-monotonic in the region below series resonant frequency. This can lead to the loss of ZVS on the primary FETs and, more critically, the loss of control. Therefore, the load is limited or clamped to  $R_{L\_dc} = 20~\Omega$ , for which the gain is monotonic (see  $\boxtimes$  12). By limiting the load, and with the max power being clamped at 6.6 kW, the power rating of the converter in BCM can be determined and is graphed in  $\boxtimes$  13.

图 13. Power Rating in Battery Charging Mode

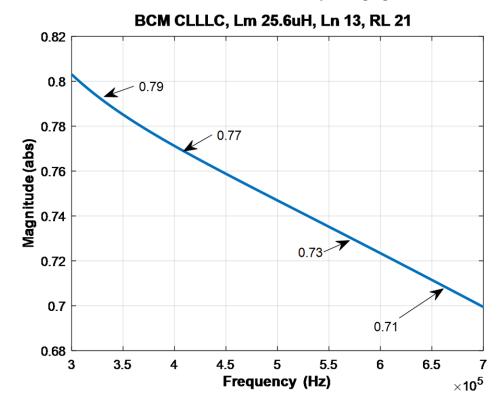

In BCM, the PFC bus voltage is set to be a ratio of 1.33 of the battery voltage. Therefore, for  $V_{batt} = 300 \text{ V}$ , the PFC bus voltage needs to be set at 400 V. Now, looking at the variation due to PFC bus ripple, with a 10% ripple on the PFC bus, the voltage will vary from 380 V to 420 V, for which the gain needed from the resonant tank will vary from 0.79 to 0.71. Based on the zoomed-in gain profile, 814, it can be determined that the frequency will vary from 330 kHz to 670 kHz.

Similarly, it can be seen that by reducing PFC ripple, the frequency variation can be reduced; for example, for a 5% bus ripple, the range is reduced to 410 kHz–570 kHz. This criteria must be taken into consideration when sizing the PFC bus capacitor.

图 14. CLLLC Tank Gain Profile, Zoomed In, for Battery Charging Mode at a Given Load

### 2.2.1.5 Discharging Mode Gain Estimate

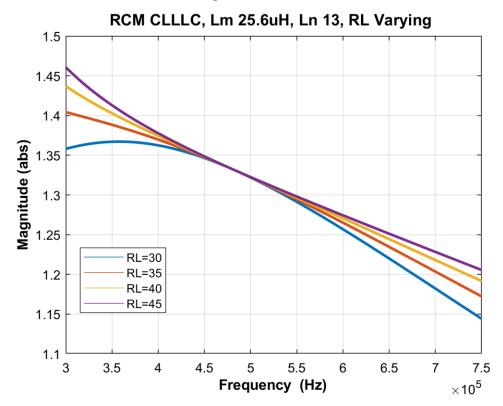

Using the equations in 节 2.2.1.1 and the tank parameters selected, the voltage gain for discharge mode can be plotted as shown in 图 15.

图 15. CLLLC Tank Voltage Gain in Reverse Power Flow Mode

With the CLLLC in discharge mode, the PFC bus voltage is set to be a ratio of 1.33 of the battery, with which at a battery of 400 V, the bus is set to be 600 V. The max power is limited by the load that is seen by the battery, which is clamped to be 30  $\Omega$  to avoid the non-monotonic region in the CLLLC gain curve. With the above clamp for the reverse power flow load, the power rating is determined as shown in  $\mathbb{Z}$  16.

图 16. Power Rating in Reverse Power Flow Mode

### 2.2.2 Current and Voltage Sensing

In the following sections, the sensing scheme for different currents and voltages on the design are discussed. On the design, multiple schemes are implemented so that users can select the appropriate one for their application needs. The calculations for the sense range are provided in the CLLLC\_calculations.xlsx.

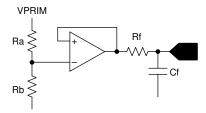

### 2.2.2.1 VPRIM Voltage Sensing

The C2000 MCU is biased on the primary side; hence, the primary voltage is sensed by a resistor divider to the ground of the board. As oversampling is used, an opamp in voltage follower arrangement is used to buffer the signal for the ADC as shown in [8] 17. The buffer helps reduce impedance as seen by the ADC, and hence, a faster sampling rate can be used. Otherwise, the sampling will be limited by the time constant of the resistor divider resistance, which is typically high, and hence, only slow sampling can be done.

### 图 17. VPRIM Voltage Sensing Circuit

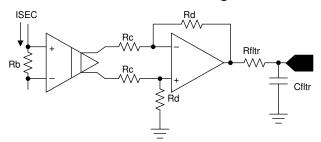

### 2.2.2.2 VSEC Voltage Sensing

The secondary side voltage is sensed in an isolated manner using the AMC1311, as shown in 🛭 18.

# VSEC Ra Rc Rc Rfltr Rc Cfltr

图 18. VSEC Voltage Sensing Circuit

### 2.2.2.3 ISEC Current Sensing

The secondary side output current is also sensed in an isolated manner using the AMC1302, as shown in

§ 19.

Also, see the TINA simulation file located under the software install directory <solution>/hardware/AMC1302\_CurrentSenseSec.TSC.

### 图 19. ISEC Current Sensing Circuit

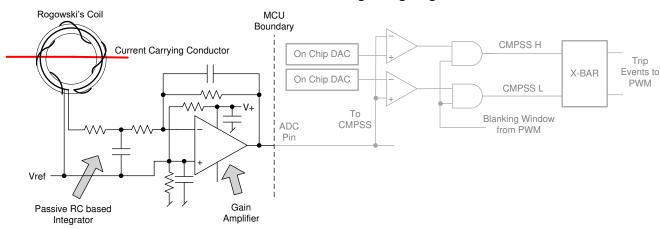

### 2.2.2.4 ISEC TANK and IPRIM TANK\_2

A Rogowski coil-based sensing mechanism is chosen to sense the high-frequency current in the tank on the primary side and the secondary side in an isolated manner, as shown in 20. The ADC pin is internally connected to the Comparator Subsystem (CMPSS), which can generate the correct pulses that go through the X-Bar to the PWM to get the action required for synchronous rectification.

图 20. ISEC Tank Current Sensing Using Rogowski's Coil

### 2.2.2.5 **IPRIM TANK**

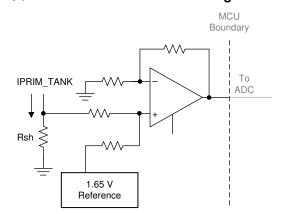

For the primary side, as the MCU is on the same ground plane, a non-isolated current scheme can also be implemented using a shunt-based sensing method, as shown in 21.

图 21. IPRIM Tank Current Sensing Circuit

### 2.2.2.6 IPRIM Current Sensing

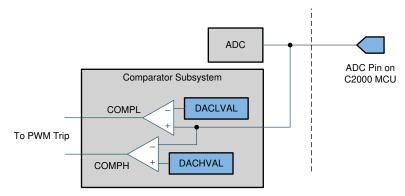

The primary return current is sensed using the on-chip Programmable Gain Amplifier (PGA). Compared to IPRIM\_TANK sensing, the on-chip resources are used to sense this current, thus enabling cost and board-space savings (see 22).

Boundary High Trip MCU Boundary Low Trip CMPSS H On Chip DAC Trip Events to X-BAR On Chip DAC PWM CMPSS L Blanking Window from PWM IPRIM To ADC IPRIM\_TANK On Chip DAC

图 22. IPRIM Current Sensing Circuit, Comparison With Typical MCU vs C2000 MCU

### 2.2.2.7 Protection (CMPSS and X-Bar)

Typical Non C2000 MCU

1.65 V Reference

Most power electronics converters need protection from overcurrent events. For this design, multiple comparators are needed, and references for the trip points need to be generated. Using C2000 MCUs—such as TMS320F280049, which has an on-chip windowed comparator as part of the Comparator Subsystem (CMPSS) along with 12-bit DACs for trip set points—that are internally connected to the PWM module enables fast tripping of the PWM without the need of external hardware. This saves board space and cost in the end application as extra components can be avoided by using on-chip resources such as DAC, comparators, and ADC. All of these resources can be used together and at the same time, without any extra external connections. Furthermore, the CMPSS-generated signals go to the X-Bar, where they can be combined in different and unique fashions to flag unique trip events from multiple sources.

C2000 MCH

### 图 23. Comparator Subsystem (CMPSS) Used for Overcurrent Protection

### 2.2.3 PWM Modulation

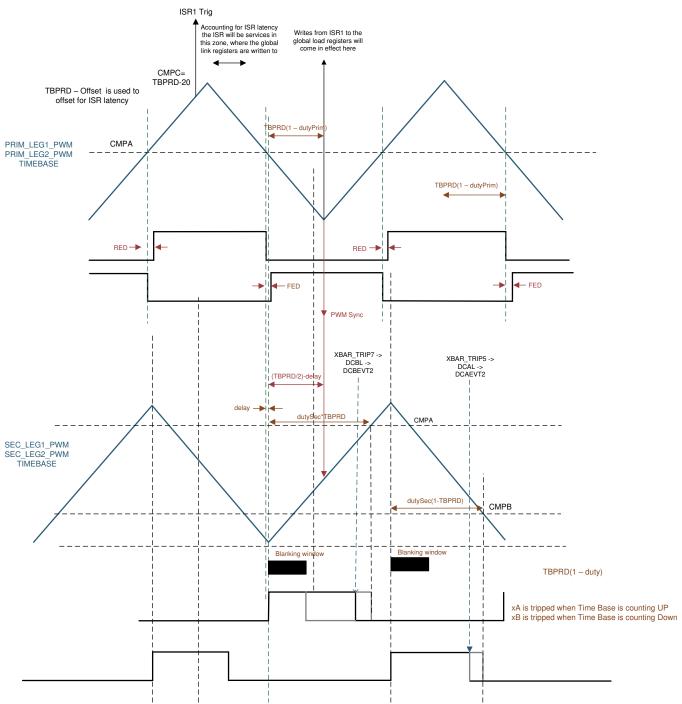

24 shows the PWM waveform configuration used on this design.

High-resolution PWM is used for the primary legs and the secondary legs. Up-down count mode is used to generate the PWMs. To use the high-resolution PWMs, the PRIM\_LEG1\_H PWM pulse is centered on the period event and the time base is configured to be up-down count. A complementary pulse with high-resolution dead time is then generated for the complementary switch. Between LEG1 and LEG2, there is a 180-degree phase shift for a full-bridge operation. This is achieved by using the feature on the PWM module to swap the xA and xB output. (Alternatively, a phase shift can also be implemented, but is not needed on this design.)

The PWM pulse to the secondary side goes through an isolator, which adds additional propagation delay. To account for this propagation delay, a small advance of the PWM is required. This is implemented in form of a phase-shift delay with respect to the primary active PWM pulse's falling edge. The phase shift of the secondary side is a combination of the period and the delay needed for the isolator, as shown in \$\mathbb{E}\$ 24. As active synchronous rectification scheme is used, the rising edge is controlled by the primary side PWM switch timing. As the switching event can be noisy, a blanking window is used. The current in the secondary tank can be discontinuous depending on the operating frequency and load. Hence, the falling edge is controlled by the trip action that is triggered as soon as the secondary current reaches zero. The trip is then latched until the next zero or period event to avoid any spurious turnon of the secondary side switches because of noise. The blanking pulse is generated by the PWM time base but the trip latch and the blanking actions happen as part of the CMPSS. Depending on whether it is the positive half or the negative half of the tank current, two different trip signals are generated and sent to the PWM module through the X-Bar. The Type-4 PWM on the C2000 MCU can uniquely use these events to trip the xA pulse during the up count and xB during the down count. For details, refer to the code in the function CLLLC HAL setupSynchronousRectificationAction(), which is the HAL file for the solution, see \(\frac{\pi}{3}\) 3.1.2.

The global link mechanism on the Type-4 PWM is used to reduce the number of cycles needed to update the registers and enables high-frequency operation. For example, the following code in the CLLLC\_HAL\_setupPWM() function links the TBPRD registers for all the PWM Legs. Using this linkage, a single write to the PRIM\_LEG1 TBPRD register will write the value to PRIM\_LEF2, SEC\_LEG1, and SEC\_LEG2.

High-resolution PWM relies on carrying forward remainder calculation from the previous cycle into the next; hence, a periodic sync should not be used between the primary and secondary side PWMs to maintain the phase relation. Whenever a frequency change or duty change is detected, a one-time sync is issued using a fast interrupt service routine (ISR1, see † 3.1.2.2).

# 图 24. PWM Scheme Used on CLLLC Design With Active Synchronous Rectification with Power Flow Primary to Secondary

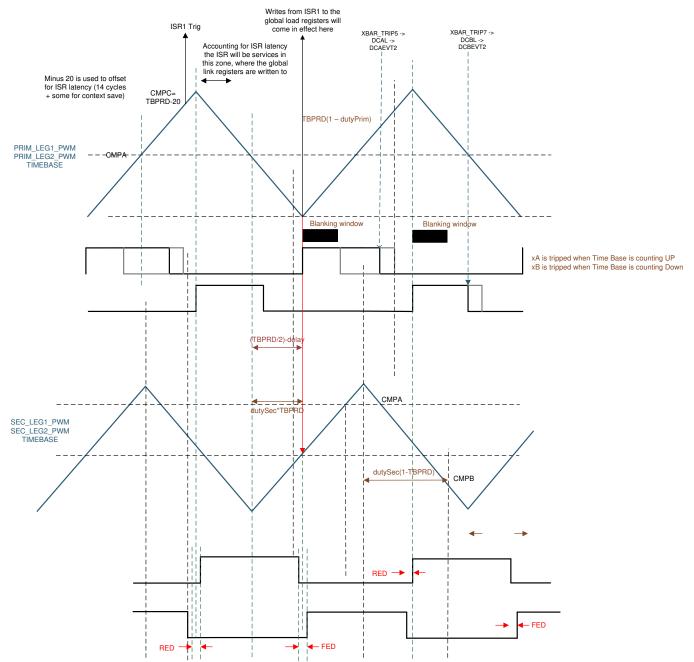

Similarly for the reverse power flow direction, the PWM configuration used is shown in 🗵 25

### 图 25. PWM Scheme Used on CLLLC Design With Active Synchronous Rectification with Power Flow Secondary to Primary

### 2.3 Highlighted Products

### 2.3.1 C2000 MCU TMS320F28004x

C2000™ 32-bit microcontrollers are optimized for processing, sensing, and actuation to improve closed-loop performance in real-time control applications such as industrial motor drives; solar inverters and digital power; electrical vehicles and transportation; motor control; and sensing and signal processing.

The TMS320F28004x (F28004x) is a powerful 32-bit floating-point microcontroller unit (MCU) that lets designers incorporate crucial control peripherals, differentiated analog, and nonvolatile memory on a single device.

The CLA allows significant offloading of common tasks from the main C28x CPU. The CLA is an independent 32-bit floating-point math accelerator that executes in parallel with the CPU. Additionally, the CLA has its own dedicated memory resources and it can directly access the key peripherals that are required in a typical control system. Support of a subset of ANSI C is standard, as are key features like hardware breakpoints and hardware task-switching.

High-performance analog blocks are integrated on the F28004x MCU to further enable system consolidation. Three separate 12-bit ADCs provide precise and efficient management of multiple analog signals, which ultimately boosts system throughput. Seven PGAs on the analog front end enable on-chip voltage scaling before conversion. Seven analog comparator modules provide continuous monitoring of input voltage levels for trip conditions.

The TMS320C2000™ devices contain industry-leading control peripherals with frequency-independent Enhanced Pulse Width Modulator/High-Resolution Pulse Width Modulator (ePWM/HRPWM) and Enhanced Capture (eCAP) module allow for a best-in-class level of control to the system. The built-in 4-channel Sigma-Delta Filter Module (SDFM) allows for seamless integration of an oversampling sigma-delta modulator across an isolation barrier.

Connectivity is supported through various industry-standard communication ports [such as Serial Peripheral Interface (SPI); Serial Communication Interface (SCI); Inter-integrated Circuit (I2C); Local Interconnect Network (LIN); and Controller Area Network (CAN)] and offers multiple muxing options for optimal signal placement in a variety of applications. New to the C2000™ platform is the fully compliant Power-Management Bus (PMBus). Additionally, in an industry first, the Fast Serial Interface (FSI) enables high-speed, robust communication to complement the rich set of peripherals that are embedded in the device.

A specially enabled device variant, TMS320F28004xC, allows access to the Configurable Logic Block (CLB) for additional interfacing features and allows access to the secure ROM, which includes a library to enable InstaSPIN-FOC<sup>™</sup>. See the Device Comparison table in the TMS320F28004x microcontrollers data manual for more information.

The Embedded Real-Time Analysis and Diagnostic (ERAD) module enhances the debug and system analysis capabilities of the device by providing additional hardware breakpoints and counters for profiling.

Following is the subset of features of the C2000 MCU that are highlighted on this design to enable control of high-frequency CLLLC topology:

1. **High-resolution PWM**: With picosecond resolutions possible, the ePWM module on the C2000 MCU can generate high-frequency PWM with accuracy. With the Type-4 PWM high-resolution period control, high-resolution duty control, high-resolution dead-band control, along with high-resolution phase shift control, is possible. This enables generation of balanced pulses for the resonant tank excitation and is an enabling feature for high-frequency power converters.

- 2. Comparator Subsystem (CMPSS) with ePWM for active synchronous rectification: Active synchronous rectification enables higher efficiency and for high-frequency resonant converters that operate both below and above the resonant point, it is a necessary feature for the topology. The C2000 MCUs' integrated CMPSS enables generation of the active synchronous rectification pulses by using the integrated comparators and the integrated Digital-to-Analog Converters (DACs). (See † 2.2.2.4.)

- 3. **Blanking window**: Due to noise, which is unavoidable in switching converters, the blanking window feature is used to suppress the CMPSS output during noisy switching events. This blanking window is provided by the ePWM time base and can be applied at different times during the PWM cycle. (See † 2.2.3.)

- 4. **X-Bar**: Multiple trip sources are possible in a power converter. The X-bar enables combining different trip actions from either different CMPSS or from GPIO to generate trip behavior desired in the ePWM without need of external logic.

- 5. **Control Law Accelerator (CLA)** enables integration of control of multiple topologies on a single controller. The software provided with this design provides the option to run the control loop on the CLA or the C28x. (See 节 3.1.2.3.)

- 6. **Global Link feature in PWM module** enables update to multiple PWMs through a single write, which reduces the CPU burden and enables higher-frequency converters to be controlled easily.

- 7. **On-chip PGA**: The on-chip PGA Is used to sense current for protection purpose on the primary side, thus enabling more cost-saving while increasing protection capability. See 节 2.2.2.6.

### 2.3.2 UCC21530-Q1

The UCC221530-Q1 is an automotive-grade, isolated dual-channel gate driver with 4-A source and 6-A sink peak current capability and a 3.3-mm channel-to-channel spacing. It is designed to drive silicon carbide (SiC) MOSFETs and insulated-gate bipolar transistors (IGBTs). Its input side is isolated from the two output drivers by a 5.7-kVRMS and 8-kV peak-reinforced isolated barrier, with a minimum of 100 V/ns Common-Mode Transient Immunity (CMTI). The internal functional isolation between the two secondary side drivers allows a working voltage of up to 850-V DC. The gate driver is also certified according to VDE, CSA, UL, CQC, and various isolation standards. Each driver accepts VDD supply voltages up to 25 V and a wide input VCCI range from 3 V to 18 V. The UCC21530-Q1 also has programmable dead-time (DT) control. An enable pin enables both outputs simultaneously when it is set high.

#### 2.3.3 AMC1311-Q1

The AMC1311 is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 7 kVPEAK according to VDE V 0884-11 and UL1577. Used in conjunction with isolated power supplies, this isolated amplifier separates parts of the system that operate on different common-mode voltage levels and protects lower-voltage parts from damage.

The high-impedance input of the AMC1311 is optimized for connection to high-voltage resistive dividers or other voltage signal sources with high output resistance. The excellent performance of the device supports accurate, low temperature drift voltage or temperature sensing and control in closed-loop systems. The integrated missing high-side supply voltage detection feature simplifies system-level design and diagnostics.

### 2.3.4 AMC1302-Q1

The AMC1302 is a precision isolated amplifier with a capacitive isolation barrier that has high immunity to magnetic interference. This barrier provides reinforced isolation of 5 kVRMS (maximum) with a very long lifetime and low power dissipation. When used with isolated power supplies, this device isolates components that operate on different common-mode voltage levels. Furthermore, the AMC1302 also protects lower-voltage devices from damage.

The input of the AMC1302 is optimized for direct connection to shunt resistors or other low voltage-level signal sources. The ±50-mV input voltage range allows significant reduction of the power dissipation through the shunt. Additionally, the low high-side supply current and voltage of the AMC1302 allow use of low-cost isolated power supply solutions. The performance of the device supports accurate current control, resulting in system-level power savings and low-torque ripple that is particularly important in motor control applications.

### 2.3.5 LMV116

The LMV116 (single) rail-to-rail output voltage feedback amplifiers offer high-speed (45 MHz) and low-voltage (2.7 V) operation in addition to micropower shutdown capability (LMV118).

Output voltage range extends to within 20 mV of either supply rail, allowing wide dynamic range especially in low-voltage applications. Even with low supply current of 600  $\mu$ A, output current capability is kept at a respectable  $\pm 20$  mA for driving heavier loads. Important device parameters such as bandwidth, slew rate, and output current are kept relatively independent of the operating supply voltage by a combination of process enhancements and design architecture.

For portable applications, the LMV118 provides shutdown capability while keeping the turnoff current to  $15~\mu A$ . Both turnon and turnoff characteristics are well-behaved with minimal output fluctuations during transitions; thus, the device can be used in power-saving mode, as well as multiplexing applications. Miniature packages (5-pin and 6-pin SOT-23) are further means to ease the adoption of these low-power, high-speed devices in applications where board area is at a premium.

### 3 Hardware, Software, Testing Requirements, and Test Results

### 3.1 Required Hardware and Software

This section details the hardware and explains the different sections on the board and how to set them up for the experiments as outlined in this design guide.

### 3.1.1 Hardware Settings

The design follows a High-Speed Edge Card (HSEC) control card concept, and any device for which a HSEC control card is available from the C2000 MCU product family can be potentially used on this design. The key resources used for controlling the power stage on the microcontroller are listed in 表 2. 图 26 shows the key power stage and connectors on the reference design. 表 3 lists the key connectors and their functions. To get started:

- 1. Make sure no power source is connected to the board.

- 2. Insert the control card in the J202-J207 slot.

- 3. Connect a power source (but do not power up) for the primary and secondary side (+5 V, 2 A) at the test points shown in 🗵 26.

- 4. Now, switch the power source on for both the primary and secondary side. A green LED on the control card will light up. This indicates the C2000 MCU device is powered. Note: The bias for the microcontroller is separated from the power stage; this enables a safe bringup of the system in this set of instructions.

- 5. To connect JTAG, use a USB cable from the control card and connect it to a host computer.

- 6. A DC power supply must be connected (*but not powered up*) for the primary side voltage (VPRIM) across J100 and J103. Typical power rating for this supply is: VDC 350 V–600 V, Power 6.6 kW. However, a lower-rating supply can be used in the case where only low-power tests are being conducted.

- 7. A second DC power source is needed to emulate a battery voltage lab, and can be connected (*but not powered up*) to J101-J102 to provide the secondary side voltage (VSEC).

- 8. Mechanism to load the secondary side is needed for an appropriate power level. For example, for a 300-V, 4-kW test, a resistive load of  $\sim$ 22.5  $\Omega$  is needed.

- 9. Current and voltage probes can be connected to observe the tank current at primary and secondary. Optionally, a power meter can be connected to measure the efficiency.

### 图 26. Board Overview

### 表 2. Key Controller Peripherals Used for Control of the Power Stage on the Board

| SIGNAL NAME  | HSEC PIN<br>NUMBER | FUNCTION                                                             |

|--------------|--------------------|----------------------------------------------------------------------|

| PWM-1A       | 49                 | PWM : PRIM_LEG1_H (Primary side leg 1, high side switch)             |

| PWM-1B       | 51                 | PWM : PRIM_LEG1_L ((Primary side leg 1,low side switch)              |

| PWM-2A       | 53                 | PWM : PRIM_LEG2_H (Primary side leg 2, high side switch)             |

| PWM-2B       | 55                 | PWM : PRIM_LEG2_L ((Primary side leg 2,low side switch)              |

| PWM-3A       | 50                 | PWM : SEC_LEG1_H (Secondary side leg 1, high side switch)            |

| PWM-3B       | 52                 | PWM : SEC_LEG1_L (Secondary side leg 1, low side switch)             |

| PWM-4A       | 54                 | PWM : SEC_LEG2_H (Secondary side leg 2, high side switch)            |

| PWM-4B       | 56                 | PWM : SEC_LEG2_L (Secondary side leg 2, low side switch)             |

| VDAC_PGA     | 9                  | DAC: 1.65 reference generated for on chip PGA bases sensing of IPRIM |

| VSEC         | 14                 | ADC                                                                  |

| IPRIM        | 15                 | PGA +                                                                |

| VPRIM        | 18                 | ADC                                                                  |

| IPRIM_TANK   | 21                 | ADC with CMPSS (dual mapped)                                         |

| IPRIM_TANK_2 | 23                 | ADC with CMPSS (dual mapped)                                         |

| ISEC_TANK    | 24                 | ADC with CMPSS (dual mapped)                                         |

| IPRIM_TANK_2 | 25                 | ADC with CMPSS (dual mapped)                                         |

| ISEC         | 27                 | ADC with CMPSS                                                       |

| IPRIM_TANK   | 28                 | ADC with CMPSS (dual mapped)                                         |

| ISEC_TANK    | 34                 | ADC with CMPSS (dual mapped)                                         |

| PRI_FAULT    | 74                 | GPIO : IO flag for the primary side                                  |

| SCI_RX       | 76                 | GPIO : Communication to PFC controller                               |

| SCI_TX       | 78                 | GPIO : Communication to PFC controller                               |

### 表 3. Key Connectors and Their Function

| CONNECTOR NAME | FUNCTION                                           |

|----------------|----------------------------------------------------|

| J100-J103      | Primary power connection                           |

| J101-J102      | Secondary power connection                         |

| J203           | Connection for communication to the PFC controller |

| J202-J207      | HSEC control card connector slot                   |

Specific to the F28004x device, the following IOs are used in the code:

- 1. Profiling code, ISR1, ISR2, ISR3 → GPIO40 (HSEC pin 68), GPIO11 (HSEC pin 70), GPIO16 (HSEC pin 67)

- 2. Debugging active synchronous rectification, the CMPSS output is brought out on XBAR1 and XBAR2 → GPIO58 (HSEC pin 99), GPIO59 (HSEC pin 101)

### 3.1.1.1 Control Card Settings

Certain settings on the device control card are required to communicate over JTAG and use the isolated UART port. The user must also provide a correct ADC reference voltage. The following are the required settings for revision A of the F280049M control card. The user can also refer to the information sheet located inside C2000Ware at \c2000ware\boards\controlcards\TMDSCNCD280049C or alternatively get it from the F280049 controlCARD Information Guide.

- 1. S1:A on the control card must be set on both ends to the "ON (up)" position to enable JTAG connection to the device and UART connection for the SFRA GUI. If this switch is set to "OFF (down)", the user cannot use the isolated JTAG built-in on the control card nor can the SFRA GUI communicate to the device.

- 2. J1:A is the connector for the USB cable that is used to communicate to the device from a host PC on which Code Composer Studio™ Integrated Development Environment (IDE) runs.

- 3. A 3.3-V reference is desired for the control-loop tuning on this design. Internal reference of the F28004x is used, and for this, the S8 switch must be moved to the left (that is, pointing to VREFHI).

- 4. A capacitor is connected between the isolated grounds on the control card, C26:A. It is advised that this capacitor be removed for the best performance of this reference design.

### 3.1.2 Software

The software of this design is available in the DigitalPower Software Development Kit (SDK) for C2000 MCUs (C2000WARE-DIGITALPOWER-SDK) and is supported inside the powerSUITE framework.

### 3.1.2.1 Opening the Project Inside Code Composer Studio

To start:

1. Install Code Composer Studio from the Code Composer Studio (CCS) Integrated Development Environment (IDE) tools folder. Version 9.3 or above is recommended.

2.

- 3. Install C2000WARE-DIGITAL-POWER-SDK in one of two ways:

- Through the C2000Ware Digital Power SDK tools folder

- Go to CCS and under View → Resource Explorer. Under the TI Resource Explorer, go to C2000WARE-DIGITAL-POWER-SDK, and click on the install button.

- 4. Once installation completes, close CCS, and open a new workspace. CCS automatically detects powerSUITE. A restart of CCS may be required for the change to be effective.

| 注: | powerSUITE is installed with the SDK by default. |  |

|----|--------------------------------------------------|--|

| 注: | powerSUITE is installed with the SDK by default. |  |

The firmware project can now be imported as follows:

Through resource explorer:

- 1. In the Resource Explorer, under C2000WARE-DIGITAL-POWER-SDK, click on powerSUITE  $\rightarrow$  Solution Adapter Tool ( ).

- 2. Select CLLLC from the list of solutions presented under DC-DC section.

- 3. The development kit page will be displayed

4.

- 1. The icon to run the project will appear in the top bar. Click Run Project.

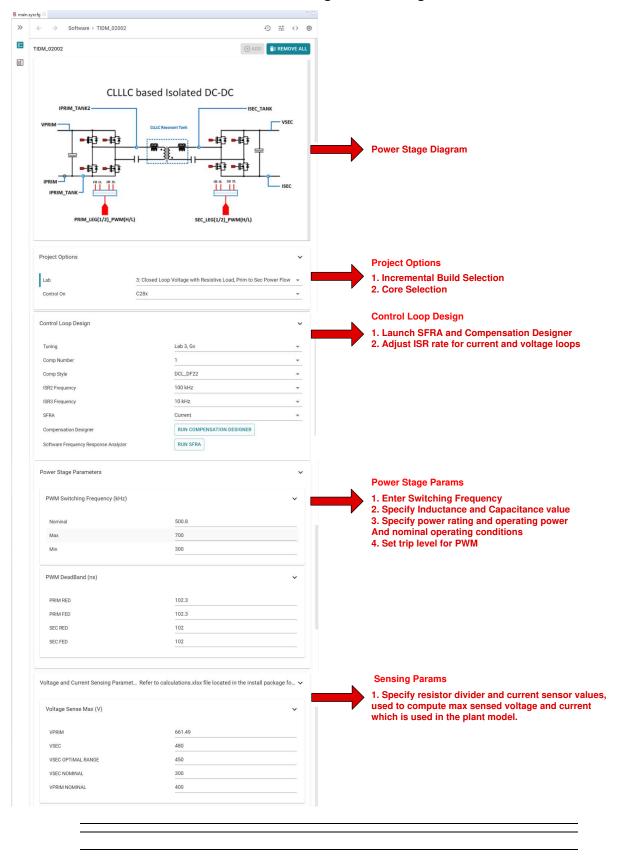

- 2. This action imports the project into the workspace environment, and a configuration page page with a GUI similar to 🛭 27 appears.

- 3. If this GUI page does not appear, refer to the FAQ section under powerSUITE in the C2000WARE-DIGITAL-POWER-SDK resource explorer.

### Direct import from the solution folder:

The user can also directly import the project, by going inside CCS to Click Project → Import CCS Projects and browsing to the solution folder located at <SDK>/solutions/tidm\_02002/f28004x/ccs.

Two project specs will appear: one of the project with powerSUITE, and the other without powerSUITE. Clicking on either will create a self-contained folder of the project with all the dependencies inside it.

The non-powerSUITE project is provided for customers who find the powerSUITE GUI limiting or want to remove powerSUITE for production code.

This document guides the user through the powerSUITE project, but all the steps can be repeated with the non-powerSUITE project with modification to the relevant #defines in the powerSUITE settings.h file, which are documented in this design guide.

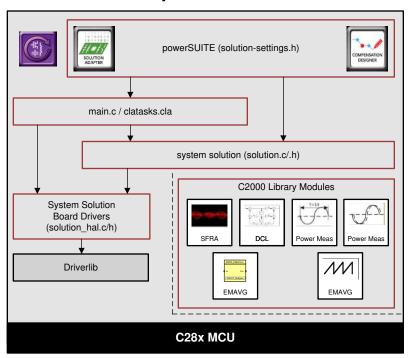

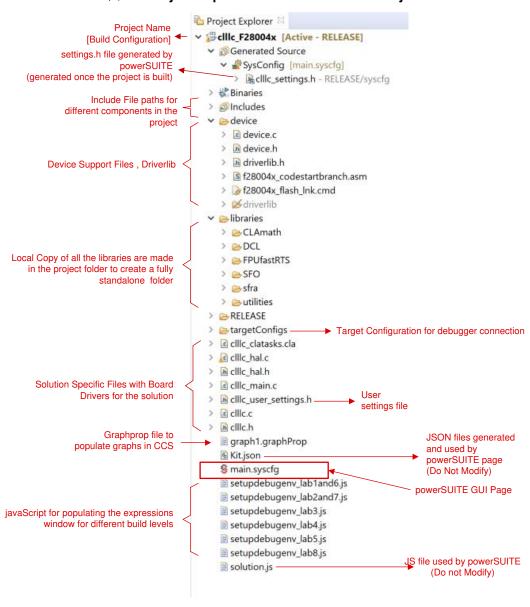

### 3.1.2.2 Project Structure

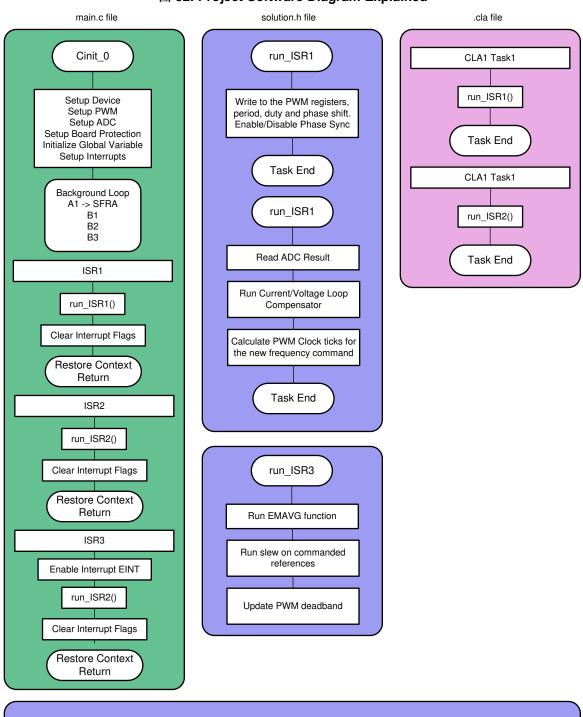

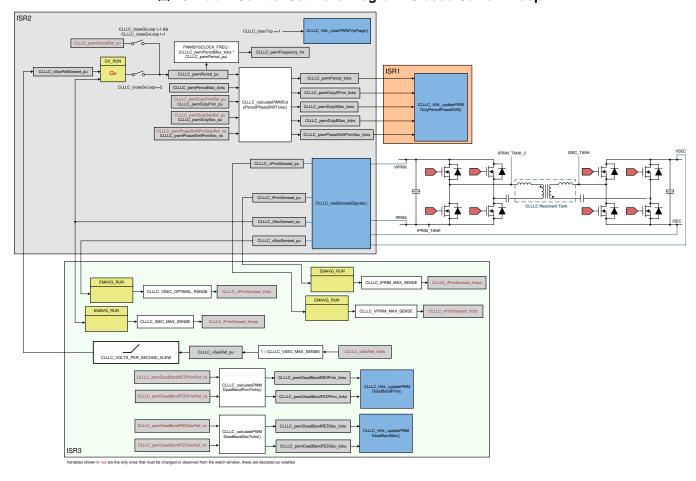

图 28. Project Structure Overview

The general structure of the project is shown in § 28. Once the project is imported, the Project Explorer will appear inside CCS as shown in § 29. Note: § 29 shows the project for F28004x; however, if a different device is chosen from the powerSUITE page, the structure will be similar.

Solution-specific and device-independent files that consist of the core algorithmic code are in "<solution>.c/h".

Board-specific and device-specific files are in "<solution>\_hal.c/h". This file consists of device-specific drivers to run the solution. If the user wants to use a different modulation scheme or a different device, the user is required only to make changes to these files, besides changing the device support files in the project.

The "<solution>-main.c" file consists of the main framework of the project. This file consists of calls to the board and solution file that help in creating the system framework, along with the interrupt service routines (ISRs) and slow background tasks.

For this design, <solution> is "clllc".

The powerSUITE page can be opened by clicking on the "main.syscfg" file, listed under the Project Explorer. The powerSUITE page generates the "<solution>\_settings.h" file. This file is the only C based file used in the compile of the project that is generated by the powerSUITE page. The user must not modify this file manually, as the changes will be overwritten by powerSUITE each time the project is saved. "<solution>\_user\_settings.h" is included by the "<solution>\_settings.h" and can be used to keep any settings that are outside the scope of powerSUITE tools such as #defines for ADC mapping, GPIOs etc.

The "Kit.json" and "solution.js" files are used internally by powerSUITE and also must not be modified by the user. Any changes to these files will result in the project not functioning properly.

The solution name is also used as the module name for all the variables and defines used in the solution. Hence, all variables and function calls are prepended by the CLLLC name (for example, CLLLC\_vSecSensed\_pu). This naming convention lets the user combine different solutions while avoiding naming conflicts.

图 29. Project Explorer View of the CLLLC Project

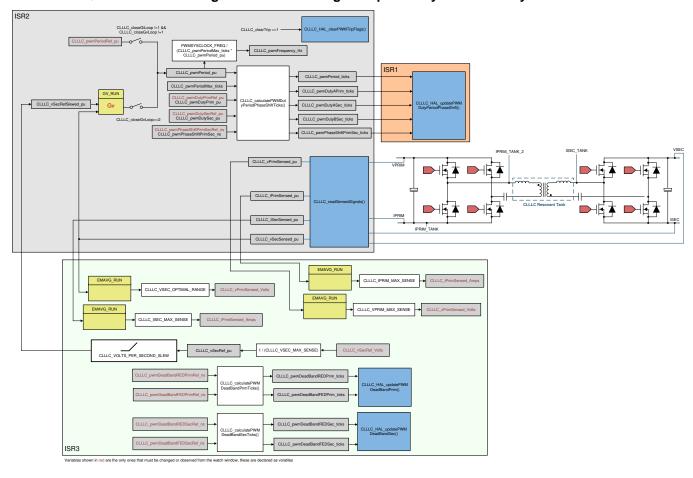

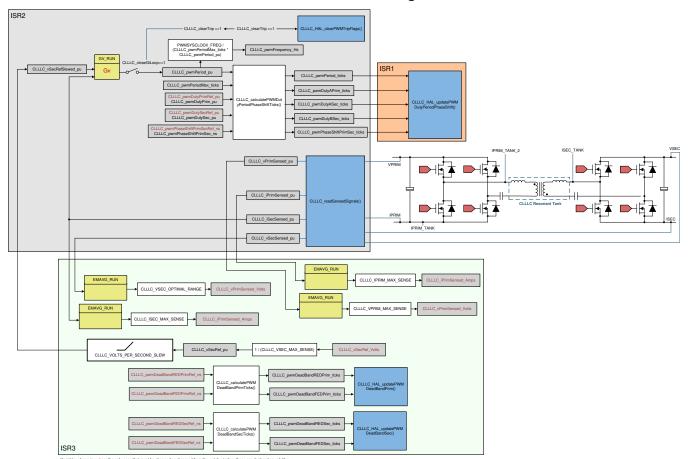

The CLLLC project consists of three **ISRs** (ISR1, ISR2, and ISR3) with ISR1 being the fastest and non-nestable ISR.

**ISR1** is reserved for the PWM update ISR. ISR1 is triggered by the PRIM\_LEG1\_PWM\_BASE → EPWM\_INT\_TBCTR\_U\_CMPC event. In general, this interrupt is disabled by writing a value to CMPC, which is greater than all possible TBPRD register values for PRIM\_LEG1\_PWM\_BASE. This is done through the CLLLC\_HAL\_setupISR1Trigger function. Following are the defines that are related to this ISR.

```

#define CLLLC_ISR1_PERIPHERAL_TRIG_BASE CLLLC_PRIM_LEG1_PWM_BASE

#define CLLLC_ISR1_TRIG INT_EPWM1

#define CLLLC_ISR1_PIE_GROUP INTERRUPT_ACK_GROUP3

#define CLLLC_ISR1_TRIG CLA CLA TRIGGER EPWM1INT

```

**ISR2** is responsible for writing a valid value to trigger ISR1 by a write to CMPC when ISR1 is desired. (Note: The CMPC is not tied to the global load mechanism to enable this. Also, shadow load of CMPC is disabled.) The CMPC value can be adjusted to get the desired timing from the ISR1. Each time ISR1 is enabled, it triggers two times. In the first ISR1, PWM registers are updated and a sync is enabled. In the second ISR1, the PWM sync is disabled and CMPC is set to a value such that ISR1 does not trigger again. For simplicity the software diagrams and structure only show ISR1 that is triggered the first time.

ISR2 is periodically triggered at ISR2\_FREQUENCY. A spare CAP module is used to generate the time base and trigger the interrupt. A spare ePWM module is also configured with the same time base and is used to trigger the ADC conversions. ISR2 is responsible for running the control law and calculating the clock ticks required for the PWM. Once the writes to the shadow registers are complete, the ISR2 enables the ISR1 trigger by writing a valid value (that is, one that is less than the current TBPRD register) to the CMPC register. ISR2 has two variants ISR2\_primToSecPowerFlow and ISR2\_secToPrimPowerFlow, one for the power flow from primary to secondary side and other for secondary to primary. This is done to to optimize CPU cycles when controlling power flow in different directions. For simplicity of explaination either of them are just referred to as ISR2 in respective labs. Depending on the timing, the ISR1 may nest ISR2 for the update writes, which are very timing-critical. Following are the defines that are related to this ISR.

```

#define CLLLC_ISR2_ECAP_BASE ECAP1_BASE

#define CLLLC_ISR2_PWM_BASE EPWM5_BASE

#define CLLLC_ISR2_TRIG INT_ECAP1

#define CLLLC_ISR2_PIE_GROUP INTERRUPT_ACK_GROUP4

#define CLLLC_ISR2_TRIG_CLA CLA_TRIGGER_ADCA2

```

**ISR3** is triggered by ADCINT2, which is initiated by a conversion that is started using a CPU timer. It is used to run housekeeping functions such as doing a running average on the currents and voltage signals to remove noise, and running the slew rate function for commanded references.

```

#define CLLLC_ISR3_TIMEBASE CLLLC_TASKC_CPUTIMER_BASE

#define CLLLC_ISR3_PERIPHERAL_TRIG_BASE ADCC_BASE

#define CLLLC_ISR3_TRIG INT_ADCC2

#define CLLLC_ISR3_PIE_GROUP INTERRUPT_ACK_GROUP10

```

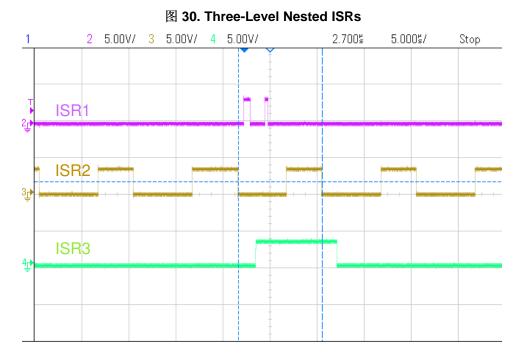

With this, the interrupts can be nested easily. 🛭 30 shows the nesting of the three interrupts occurring. The image is taken for the system in open loop and when a period change is initiated through the watch window, hence only one time ISR1 trigger is observed. For a closed-loop system, the period will only have minor changes from one control ISR cycle to the other and hence the ISR1 will be triggered repeatedly.

Additionally, CPU timers are used to trigger slow background tasks (these are not interrupt-driven but polled).

"A" tasks are triggered at TASKA\_FREQ, which is 100 Hz. The SFRA GUI must be called at this rate. One task, A1, is executed at this rate.

"B" tasks are triggered at TASKB\_FREQ, which is 10 Hz. These are used for some basic LED toggles and state machine items that are not timing-critical. Three tasks—B1, B2, B3—are serviced by this; hence, each has an execution rate of 3.33 Hz.

```

#define TASKA_FREQ 100

#define TASKB_FREQ 10

```

The software of this reference design is organized in eight labs, with incremental builds (INCR\_BUILD) and project options (CLLLC\_CONTROL\_MODE,

CLLLC\_SEC\_CONNECTED\_IN\_BATTERY\_EMULATION\_MODE). These tests simplify the system bringup and design.

Lab 1: Primary to Secondary Power Flow, Open Loop Check PWM driver, no high power applied to the board. See 节 3.2.2.1

**Lab 2:** Primary to Secondary Power Flow, Open Loop Check PWM driver and ADC with protection, resistive load connected on secondary. See 节 3.2.2.2.

**Lab 3:** Primary to Secondary Power Flow, Closed Voltage Loop Check, with resistive load connected on secondary. See 节 3.2.2.3.

**Lab 4:** Primary to Secondary Power Flow, Closed Current Loop Check, with resistive load connected on secondary. See 节 3.2.2.4.

**Lab 5:**Primary to Secondary Power Flow, Closed Current Loop Check, with resistive load connected on secondary in parallel to a voltage source to emulate a battery connection on secondary side. See † 3.2.2.5.

**Lab 6:** Secondary to Primary Power Flow, Open Loop Check PWM driver, no high power applied to the board. See  $\ ^{\ddagger}$  3.2.2.6

**Lab 7:** Secondary to Primary Power Flow, Open Loop Check PWM driver and ADC with protection, resistive load connected on primary. See 节 3.2.2.7

**Lab 8:** Secondary to Primary Power Flow, Closed Voltage Loop Check, with resistive load connected on primary. See 节 3.2.2.8

These defines are in the "settings.h" file, and can be changed through the powerSUITE settings page.

#### 3.1.2.3 Using CLA on C2000 MCU to Alleviate CPU Burden

The control law accelerator (CLA) is a coprocessor available on the C2000 MCU family of devices. This coprocessor enables offloading the control-ISR functions from the main C28x CPU core. To run the control ISR on the CLA for solutions supported in powerSUITE, selection is achieved through a drop-down menu on the powerSUITE SYSCFG page.

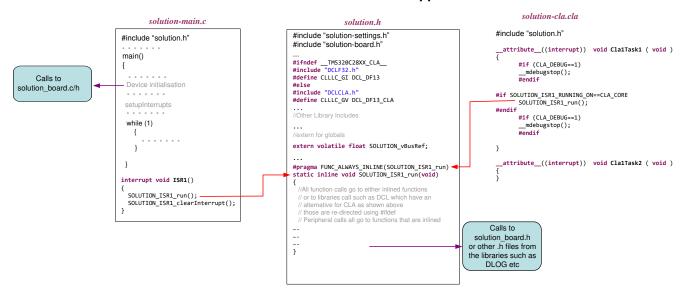

The software structure of the powerSUITE solution is designed such that offloading the task to the CLA is simply a drop-down menu selection. The code is not duplicated and a single source for the solution algorithm is maintained even when code is run on the CLA or the C28x, see 图 31. To enable single source development, the code is kept inside the "solution.h" file. This enables the CLA task to see the source and compile it for the CLA.

The CLA features of each device vary slightly. For example, on the F2837xD, F2837xS, and F2807x devices, the CLA can support only one task at a given time, and there is no nesting capability. This configuration means that the task is not interruptible. Only one ISR can be offloaded to the CLA. On the F28004x, the CLA supports a background task from which a regular CLA task can nest. This configuration enables offloading two ISRs on the CLA.

图 31. Software Architecture to Support CLA

On this design, ISR1 and ISR2 are offloaded to the CLA when the selection to run the system on CLA is made. On the F28004x, the CPU use is approximately 42% for the 100-kHz loop (not including advanced options such as phase-shedding, adaptive dead time, SFRA running, and so forth) and 11% for the 10-kHz loop that runs the voltage loop and instrumentation functions. Thus, the total CPU use is approximately 53%. With the CLA option, the CPU burden is reduced to 0% when both ISRs are offloaded to the CLA. For more information on the CLA, visit the Control Law Accelerator (CLA) Hands-On Workshop website and refer to the respective device technical reference manuals.

To enable single source development, the code for the ISR1 and ISR2 run is kept inside the "solution.h" file. This enables the CLA task to see the source and compile it for the CLA. (As ISR3 is not run on the CLA, code for ISR3 is kept inside the "solution.c" file.) This is shown in the project software diagram, 图 32.

#### 图 32. Project Software Diagram Explained

Board.c/h file provide the necessary drivers for the solution.c/h, the main.c and the .cla file to run

#### 3.2 Testing and Results

#### 3.2.1 Test Setup (Initial)

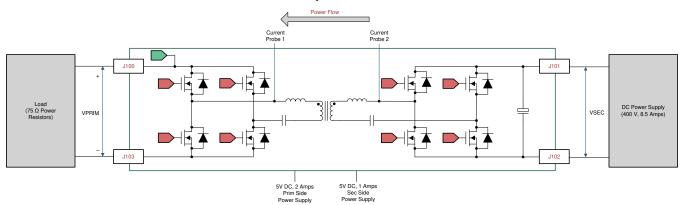

Hardware test setup is shown in 图 33 to begin testing this design. Detailed hardware setup is described in 节 3.1.1.

# DC Power Supply (400 V, 8.5 Amps) Power Flow Sty DC, 2 Amps Prim Side Power Supply Power Supply

图 33. Hardware Setup to Run Software

#### 3.2.2 Test Procedure

#### 3.2.2.1 Lab 1. Primary to Secondary Power Flow, Open Loop Check PWM Driver

This lab option is primarily provided as a focused test just for the PWM from a software perspective so that it can be ran independent of the hardware connections of the reference design. With this lab the user can run the code on a C2000 control card or launchpad just to observe the PWM waveforms.

Steps used to load and run are similar to 节 3.2.2.2.

This lab can be easily skipped and the user can go to Lab 2 directly if no changes to the PWM driver are anticipated. Hence this lab procedure is not documented as it is primarlily for PWM driver development and debug purpose.

# 3.2.2.2 Lab 2. Primary to Secondary Power Flow, Open Loop CheckPWM Driver and ADC with protection, Resistive Load Connected on Secondary

In this build, the board is excited in open-loop fashion with a specified frequency that can be changed through the watch window. The frequency is controlled with the CLLLC\_pwmPeriodRef\_pu variable.

This build verifies the sensing of feedback values from the power stage and also operation of the PWM gate driver, and ensures there are no hardware issues. Additionally, calibration of input and output voltage sensing can be performed in this build.

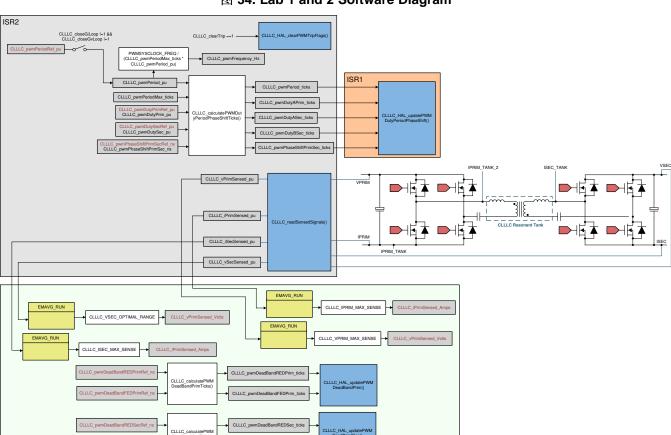

34 shows the software structure for this build.

#### 图 34. Lab 1 and 2 Software Diagram

ISR3

#### 3.2.2.2.1 Setting Software Options for Lab 2

- 1. To get started, open the CCS project, as outlined in  $\ddagger$  3.1.2.1. If using the powerSUITE page, go to step 2, otherwise jump to step 3.

- 2. Open the SYSCFG page and select under the "Project Options" section:

- "Lab 2: Open Loop PWM with Protection, Prim to Sec Power Flow" for the Lab

- Under "Tuning", select SFRA to run on the voltage to measure the voltage loop plant. Save the page.

- 3. The following defines are set in the "settings.h" file for this build. These will be set by the powerSUITE page automatically.

```

#if CLLLC_LAB == 2

#define CLLLC_CONTROL_RUNNING_ON C28x_CORE

#define CLLLC_POWER_FLOW CLLLC_POWER_FLOW_PRIM_SEC

#define CLLLC_INCR_BUILD CLLLC_OPEN_LOOP_BUILD

#define CLLLC_TEST_SETUP CLLLC_TEST_SETUP_RES_LOAD

#define CLLLC_PROTECTION CLLLC_PROTECTION_ENABLED

#define CLLLC_SFRA_TYPE CLLLC_SFRA_VOLTAGE

#define CLLLC_SFRA_AMPLITUDE (float32_t)CLLLC_SFRA_INJECTION_AMPLITUDE_LEVEL2

#endif

```

#### 3.2.2.2.2 Building and Loading the Project and Setting up Debug Environment

- 1. Right-click on the project name and click "Rebuild Project".

- 2. The project will build successfully.

- 3. In the Project Explorer, make sure the correct target configuration file is set as Active under targetConfigs (see 29).

- Then, click "Run → Debug" to launch a debugging session. In case of dual-CPU devices, a window

may appear for the user to select the CPU on which the debug is to be performed. In this case, select

CPU1.

- 5. The project will then load on the device and the CCS debug view will become active. The code will halt at the start of the main routine.

- 6. To add the variables in the watch/expressions window, click View → Scripting Console to open the scripting console dialog box. On the upper right corner of this console, click on "open" and then browse to the "setupdebugenv\_lab2and7.js" script file located inside the project folder. This will populate the watch window with the appropriate variables needed to debug the system.

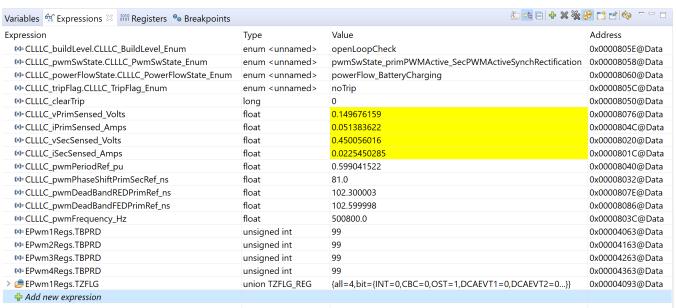

- 7. Click on the Continuous Refresh button on the watch window to enable continuous update of values from the controller. The watch window will appear as shown in 35.

图 35. Lab 2 Expression Window

#### 3.2.2.2.3 Using Real-time Emulation

Real-time emulation is a special emulation feature that allows windows within Code Composer Studio to be updated *while the MCU is running*. This allows graphs and watch views to update, but also allows the user to change values in watch or memory windows, and see the effect of these changes in the system without halting the processor.

- 1. Enable real-time mode by hovering your mouse on the buttons on the horizontal toolbar and clicking the Enable Silicon Real-time Mode (service critical interrupts when halted, allow debugger accesses while running) button.

- 2. A message box *may* appear. If so, select YES to enable debug events. This will set bit 1 (DGBM bit) of status register 1 (ST1) to a "0". DGBM is the debug enable mask bit. When the DGBM bit is set to "0", memory and register values can be passed to the host processor for updating the debugger windows.

#### 3.2.2.2.4 Running the Code

- 1. Run the project by clicking

- 2. Now, clear the trip by writing "1" to the CLLLC\_clearTrip variable.

- 3. In the watch view, check if the CLLLC\_vPrimSensed\_Volts, CLLLC\_iPrimSensed\_Amps, CLLLC\_vSecSensed\_Volts, and CLLLC\_iSecSensed\_Amps variables are updating periodically. (Note: As no power is applied right now, these will be close to zero.)

- 4. Now, slowly increase the input VPRIM DC voltage from 0 V to 400 V. Make sure CLLLC\_vPrimSensed\_Volts displays the correct values.

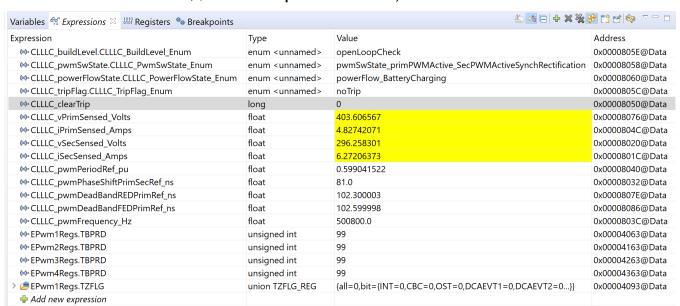

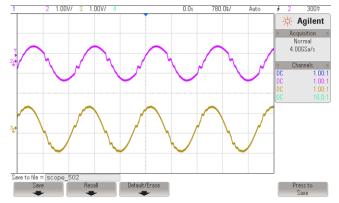

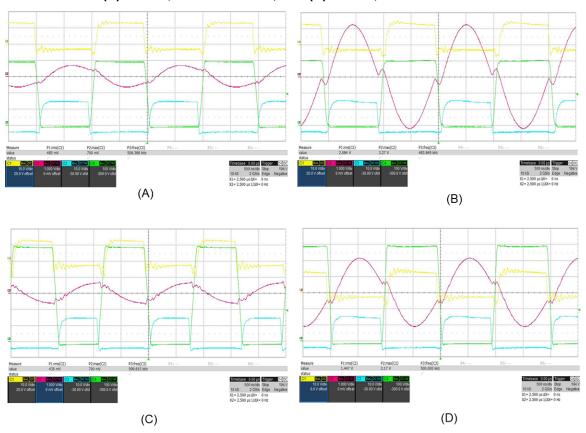

- 5. By default, the CLLLC\_pwmPeriodRef\_pu variable is set to 0.599, as shown in 🖺 36, which is 500.8 kHz. This is close to the series resonant frequency of the converter; however, due to variation in the components on the actual hardware, it can be lower or higher than the series resonant frequency. For example, in 🖺 37, we see frequency slightly lower than series resonant frequency.

图 36. Lab 2 Expression Window, at Resonance

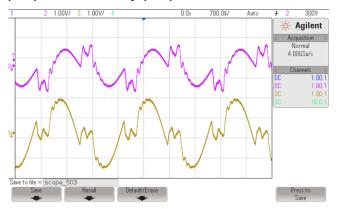

图 37. Lab 2, Primary (ch2) and Secondary (ch3) Currents at Resonance

- 6. The VSEC variable will show a voltage of close to 300 V per the tank gain designed. Verify that CLLLC\_vSecSensed\_Volts shows the correct voltage. This verifies the voltage sensing on the board.

- 7. With the load specified in the test conditions, the current from the PRIM and SEC side will be close to 4.8 A for CLLLC\_iPrimSensed\_Amps, and 6.8 A for CLLLC\_iSecSensed\_Amps.

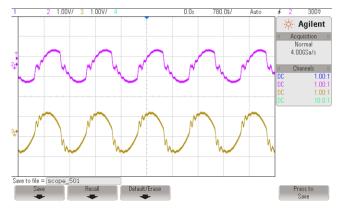

8. Next, to see operation under different frequencies (that is, above resonance, below resonance), change the CLLLC\_pwmPeriodRef\_pu variable to be 0.47 which will correspond to a frequency of 639 kHz. The waveform under this condition is shown in

38.

#### 图 38. Lab 2, Primary (ch2) and Secondary (ch3) Currents Above Series Resonance Frequency

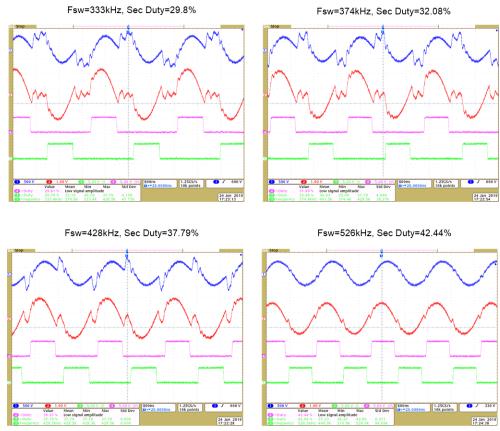

9. Next, test behavior with lower than series resonant frequency by entering 0.8 as the CLLLC\_pwmPeriodRef\_pu, which will make generate frequency of 374kHz. In this case, the primary current will become discontinuous and the secondary side duty cycle will modulate to achieve diode emulation shown in 39.

#### 图 39. Lab 2, Primary (ch2) and Secondary (ch3) Currents Below Series Resonance Frequency

10. This verifies at a basic level the PWM driver and connection of hardware.

#### 3.2.2.2.5 Measure SFRA Plant for Voltage Loop

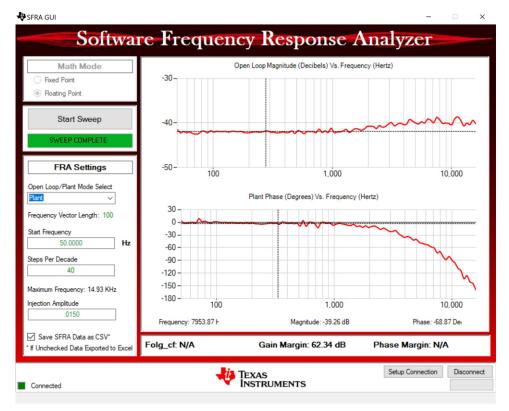

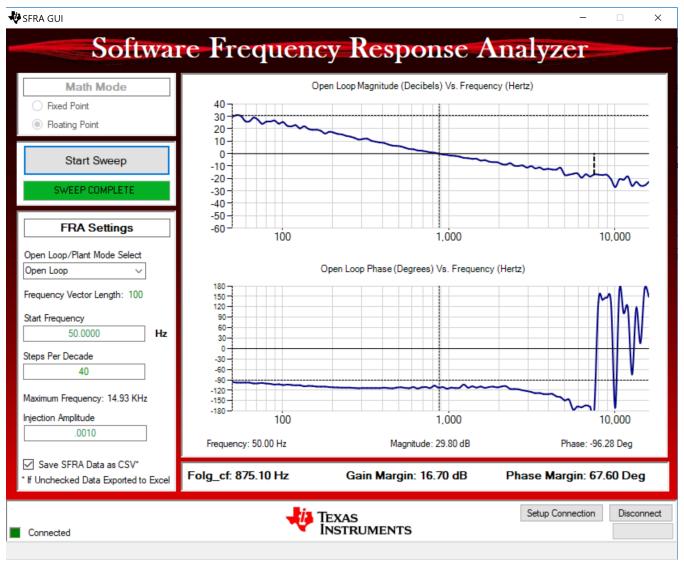

- 1. The SFRA is integrated in the software of this build to measure the plant response which can then be used to design a compensator. To run the SFRA, keep the project running, and from the SYSCFG page, click on the SFRA icon. The SFRA GUI will pop up.

- Select the options for the device on the SFRA GUI; for example, for F280049, select floating point.

Click on setup connection. In the pop-up window, uncheck the boot-on-connect option and select an appropriate COM port. Click Ok. Return to the SFRA GUI and click Connect.

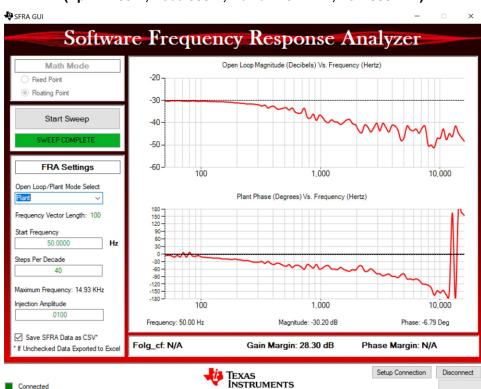

- 3. The SFRA GUI will connect to the device. A SFRA sweep can now be started by clicking "Start Sweep". The complete SFRA sweep will take a few minutes to finish. Activity can be monitored by seeing the progress bar on the SFRA GUI and also by checking the flashing of blue LED on the back of the control card, which indicates UART activity. Once complete, a graph with the measurement will appear, as shown in 40. (Note that the open-loop measurement is not valid in the lab as the loop is not closed. The user must only refer to the plant measurement.)

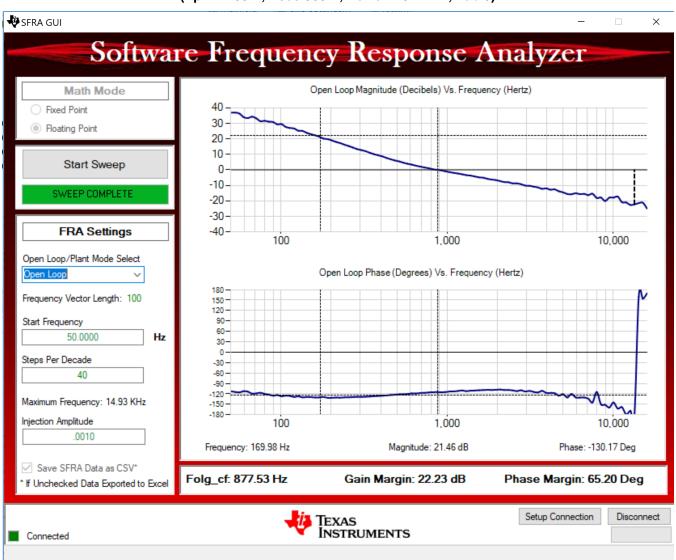

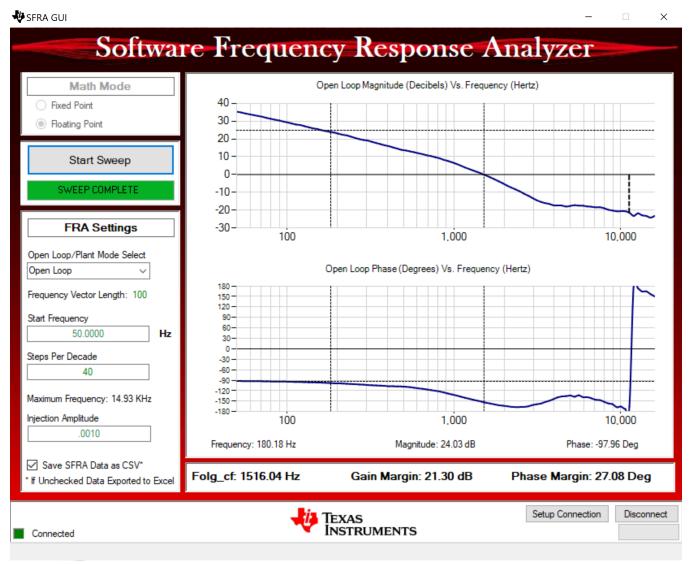

图 40. SFRA Open Loop Plot for the Closed Voltage Loop (Vprim 400 V, Vsec 300 V, Power 1.972 kW, Fsw 500 kHz)

The Frequency Response Data is also saved in the project folder, under an SFRA Data Folder, and is time-stamped with the time of the SFRA run. SFRA can be run at different frequency set points to cover the range of operation of the system. A compensator will be designed using these measured plots in the next lab; therefore, remember this timestamp, or rename the "SFRA.csv" file to a convenient name that is easy to identify.

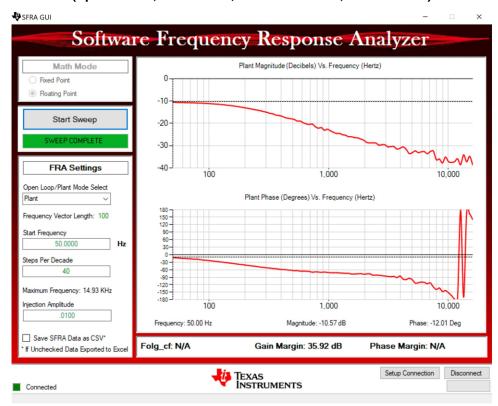

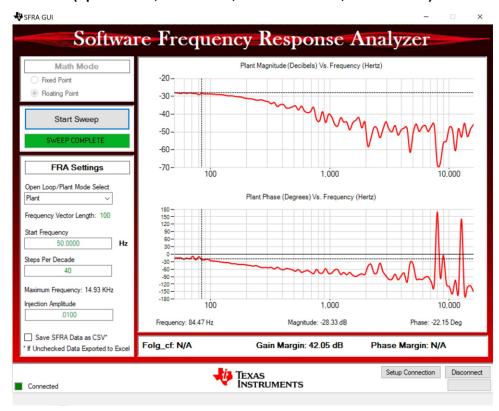

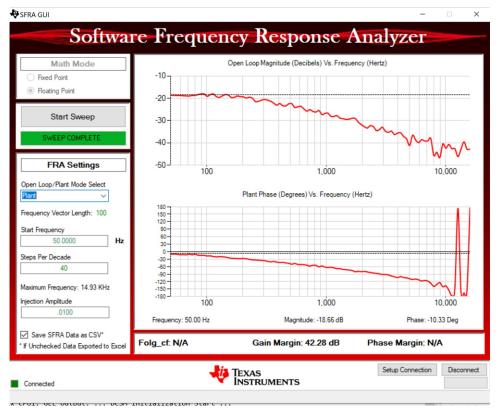

Repeat the analysis at different frequency points, the plant gain will be different at different frequency points, see 41 for gain measured at 333kHz and see 42 for gain measured at 680kHz. Hence a compensator needs to be chosen that will be stable across the frequency range of the converter. All the runs will be saved in CSV file and can then be imported into compensation designer to check stability across the range of operation.

# 图 41. SFRA Open Loop Plot for the Closed Voltage Loop (Vprim 400 V, Vsec 320 V, Power 2.174 kW, Fsw 333 kHz)

# 图 42. SFRA Open Loop Plot for the Closed Voltage Loop (Vprim 400 V, Vsec 293 V, Power 1.828 kW, Fsw 680 kHz)

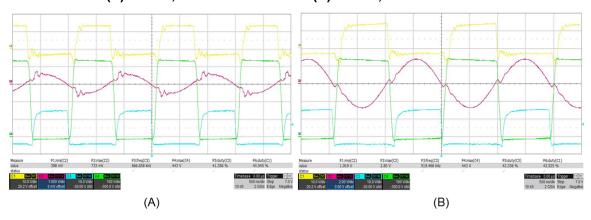

#### 3.2.2.2.6 Verify Active Synchronous Rectification

1. Optionally, to verify active synchronous rectification, the user can also probe the PWM signals and see the change in duty cycle. To connect the probe for it, the user must first stop the power stage as outlined below and de-energize all circuits under test.

## lacksquare 43. Active Synchronous Rectification Check, ch1 ightarrow IPRIM\_TANK, ch2 ightarrow ISEC\_TANK, ch3/ch4 ightarrow SEC\_LEG1\_PWMH/L

- 2. Once finished, reduce the input voltage, VPRIM, to zero. Watch for the voltages in the watch window to reduce down to zero.

- 3. Fully halting the MCU when in real-time mode is a two-step process. First, halt the processor by using the Halt button on the toolbar , or by using Target → Halt. Then, take the MCU out of real-time mode by clicking on . Finally, reset the MCU ...

- 4. Close the CCS debug session by clicking on Terminate Debug Session \_\_\_\_ (Target → Terminate all).

#### 3.2.2.2.7 Measure SFRA Plant for Current Loop

- 1. Now, return to the SYSCFG page, and select current in the SFRA options to measure the current loop plant.

- 2. Rebuild the project, and reload the project. Repeat step 3 (in 节 3.2.2.2.1) to step 2 (in 节 3.2.2.2.5). This time, the SFRA sweep will measure the plant for the current loop. Save this CSV file for use later in the Lab 3. The user can measure this at multiple points to ensure all operating conditions are covered, 图 44shows the measurement of the current loop plant at 500kHz.

### 图 44. SFRA Plant Measurement for the Current Loop at Vprim 400V, Vsec 295V, Switching Frequency at 500kHz and 1887W

- 3. This completes the check for this build, the following items are verified on successful completion of this build:

- a. Sensing of voltages and currents and scaling to be correct

- b. Interrupt generation and execution of the build 1 code in ISR1, ISR2, and ISR3

- c. PWM driver and switching

- d. Plant measurement for current and voltage loop

If any issue is observed, a careful inspection of the hardware may be required to eliminate any build issues.

- 4. The controller can now be halted and the debug connection terminated.

- 6. Close the CCS debug session by clicking on Terminate Debug Session  $\frac{\blacksquare}{\blacksquare}$  (Target  $\rightarrow$  Terminate all).

# 3.2.2.3 Lab 3. Primary to Secondary Power Flow, Closed Voltage Loop Check, With Resistive Load Connected on Secondary

In this lab, the voltage loop,  $G_v$ , is closed with a resistive load at the output.  $\boxtimes$  45 shows the complete software diagram for this build. Hardware is assumed to be set up as shown in  $\boxtimes$  33.

####

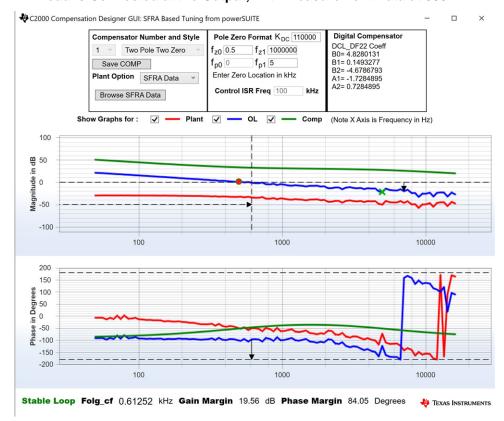

#### 3.2.2.3.1 Setting Software Options for Lab 3

- 2. **powerSUITE Settings**: On the powerSUITE page,

- a. Select under the "Project Options" section "Lab 3: Closed Loop Voltage with Resistive Load, Prim to Sec Power Flow" for the Lab.

- b. Under "Tuning", select SFRA to run on the voltage loop using the drop-down box. Save the page.

- 3. Under Control Loop Design, options for the current loop tuning will automatically be selected, Tuning → Comp Number 1 → DF22.

- 4. Save the page by "Ctrl-S" and click on the Compensation Designer button =

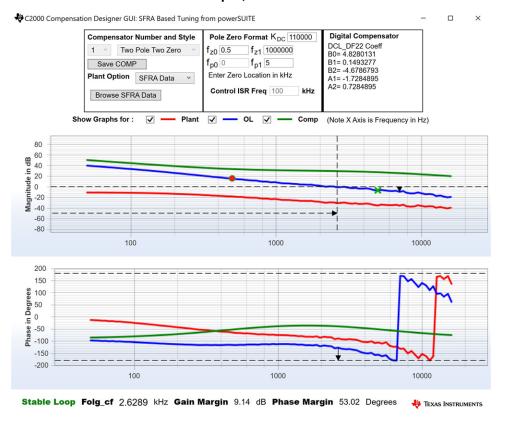

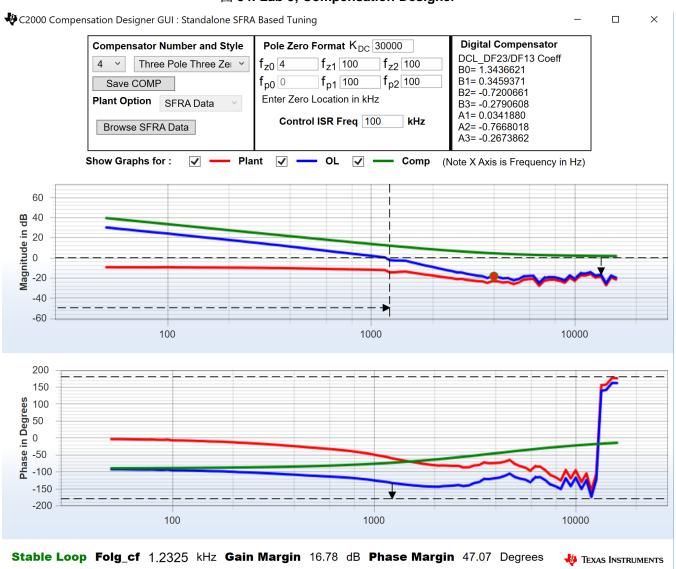

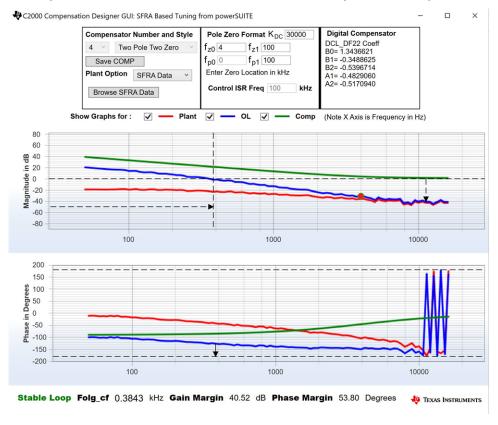

- 5. The compensation designer will then launch and prompt the user to select a valid SFRA data file. Import the SFRA data from the run in Lab 1 into the compensation designer to design a two-pole, two-zero compensator. It is good to keep more margins during this iteration of the design to ensure that when the loop is closed, the system is stable. Plant data from different runs of the SFRA can be checked to get a stable system under all conditions, for example two runs at 500kHz and 300kHz with the designed compensator are shown to be stable in § 46 and § 47.

# 图 46. Compensator Design With SFRA Based Plant Measurement for the Voltage Loop When Resistive Load is Connected at the Output, With Measurement Data at 500kHz

## 图 47. Compensator Design With SFRA Based Plant Measurement for the Voltage Loop When Resistive Load is Connected at the Output, With Measurement Data at 333kHz

- 注: The tuning is carried out in DF22 fashion; however, we run the DF13 in the software. This is done because soft-starting the DF13 is easier, whereas not possible with the DF22 structure. The coefficients in both cases remain the same. At the writing of this document, the DF12 structure is not available in DCL.

- 6. Once satisfied with the compensator design, click on "Save COMP". This will save the compensator values into the project.

- 7. Close the compensation designer, return to the powerSUITE page, and save ("Ctrl-S"). This will write the new compensator values to the "settings.h" file.

8. The following defines are set in the "settings.h" file for this build. These will be set by the powerSUITE page automatically; otherwise, edit the page manually.

```

#if CLLLC_LAB == 3

#define CLLLC_CONTROL_RUNNING_ON C28x_CORE

#define CLLLC_POWER_FLOW CLLLC_POWER_FLOW_PRIM_SEC

#define CLLLC_INCR_BUILD CLLLC_CLOSED_LOOP_BUILD

#define CLLLC_CONTROL_MODE CLLLC_VOLTAGE_MODE

#define CLLLC_TEST_SETUP CLLLC_TEST_SETUP_RES_LOAD

#define CLLLC_PROTECTION CLLLC_PROTECTION_ENABLED

#define CLLLC_SFRA_TYPE CLLLC_SFRA_VOLTAGE

#define CLLLC_SFRA_AMPLITUDE (float32_t)CLLLC_SFRA_INJECTION_AMPLITUDE_LEVEL1

```

#### 3.2.2.3.2 Building and Loading the Project and Setting up Debug Environment

- 1. Now, right-click on the project name and click "Rebuild Project".

- 2. The project will build successfully.

- 3. Click "Run → Debug" to launch a debugging session. In case of dual-CPU devices, a window may appear for the user to select the CPU on which the debug is to be performed. In this case, select CPU1.

- 4. The project will then load on the device and the CCS debug view will become active. The code will halt at the start of the main routine.

- 5. To add the variables in the watch/expressions window, click View → Scripting Console to open the scripting console dialog box. On the upper right corner of this console, click on "open" to browse to the "setupdebugenv\_lab3.js" script file located inside the project folder. This will populate the watch window with the appropriate variables needed to debug the system.

- 6. Click on the Continuous Refresh button 4 on the watch window to enable continuous update of values from the controller.

- 7. Enable real-time mode by hovering your mouse on the buttons on the horizontal toolbar and clicking

Enable Silicon Real-time Mode (service critical interrupts when halted, allow debugger accesses while running)

#### 3.2.2.3.3 Running the Code

- 1. Run the project by clicking

- 2. Now, clear the trip by writing "1" to the CLLLC\_clearTrip variable. The converter will operate in open loop as the CLLLC\_closeGvLoop variable is not yet set to "0". As there is no soft start implemented in the firmware, first soft-start the voltages on the primary and secondary sides manually.

- 3. In the watch view, check if the CLLLC\_vPrimSensed\_Volts, CLLLC\_iPrimSensed\_Amps, CLLLC\_vSecSensed\_Volts, and CLLLC\_iSecSensed\_Amps variables are updating periodically. (Note: As no power is applied right now, these will be close to zero.)

- 4. Now, slowly increase the input PRIM DC voltage from 0 V to 400 V to soft-start the converter. Make sure CLLLC\_vPrimSensed\_Volts displays the correct values for VPRIM (that is, close to 400 V).

- 5. By default, the CLLLC\_pwmPeriodRef\_pu variable is set to 0.599, which is 500.8 kHz. This is close to the series resonant frequency of the converter; however, due to variation in the components on the actual hardware, it can be lower or higher than the series resonant frequency.

- 6. For the 400-V primary input, with turns ratio being 1.33, the CLLLC\_vSecSensed\_Volts variable will be close to 300 V. Set the CLLLC\_vSecRef\_Volts variable to be 300 V.

- 7. Now, set the CLLLC\_closeGvLoop variable to "1". This will close the voltage loop and the controller will now try to regulate the voltage.

- 8. Test the closed-loop operation by varying CLLC\_vSecRef\_Volts from 295 V to 320 V. The user will observe that the CLLLC\_vSecSensed\_Volts will track this command reference. The converter will operate below series resonant, at resonance, and above resonance. Now, change the voltage back to 300 V to run the SFRA.

#### 3.2.2.3.4 Measure SFRA for Closed Voltage Loop

- 1. The SFRA is integrated in the software of this build to verify that the designed compensator provides enough gain and phase margin by measuring on hardware. To run the SFRA, keep the project running, and from the SYSCFG page, click on the SFRA icon. The SFRA GUI will pop up.

- 2. Select the options for the device on the SFRA GUI; for example, for F280049, select floating point. Click on setup connection. In the pop-up window, uncheck the boot-on-connect option and select an appropriate COM port. Click Ok. Return to the SFRA GUI and click Connect.

- 3. The SFRA GUI will connect to the device. A SFRA sweep can now be started by clicking "Start Sweep". The complete SFRA sweep will take a few minutes to finish. Activity can be monitored by seeing the progress bar on the SFRA GUI and also by checking the flashing of blue LED on the back of the control card, which indicates UART activity. Once complete, a graph with the open loop plot will appear, as shown in 48.

#### 图 48. SFRA Open Loop Plot for the Closed Voltage Loop (Vprim 400 V, Vsec 300 V, Power 1.972 kW, with Resistive Load at the Output)

The Frequency Response Data is also saved in the project folder, under an SFRA Data Folder, and is time-stamped with the time of the SFRA run.

The data matches closely to the designed compensator, but it is reasonable to expect deviations because the measurement in open loop is susceptible to error, due to small signal injection, which can drift the DC point of the converter.

Test the SFRA at different voltages to verify that the system is stable across the operable range.

- 4. This verifies the voltage loop design.

- 5. To bring the system to a safe stop, bring the input VPRIM voltage down to zero. Observe the voltages and currents on the watch window go down to zero.

- 6. Fully halting the MCU when in real-time mode is a two-step process. First, halt the processor by using the Halt button on the toolbar , or by using Target → Halt. Then, take the MCU out of real-time mode by clicking on . Finally, reset the MCU .

- 7. Close the CCS debug session by clicking on Terminate Debug Session  $\stackrel{\blacksquare}{}$  (Target  $\rightarrow$  Terminate all).

# 3.2.2.4 Lab 4. Primary to Secondary Power Flow, Closed Current Loop Check, With Resistive Load Connected on Secondary

In this lab, the output current control loop is closed.

49 shows the complete software diagram for this build. Hardware is assumed to be set up as shown in

33.

图 49. Lab 4 Control Software Diagram: Closed Current Loop

#### 3.2.2.4.1 Setting Software Options for Lab 4

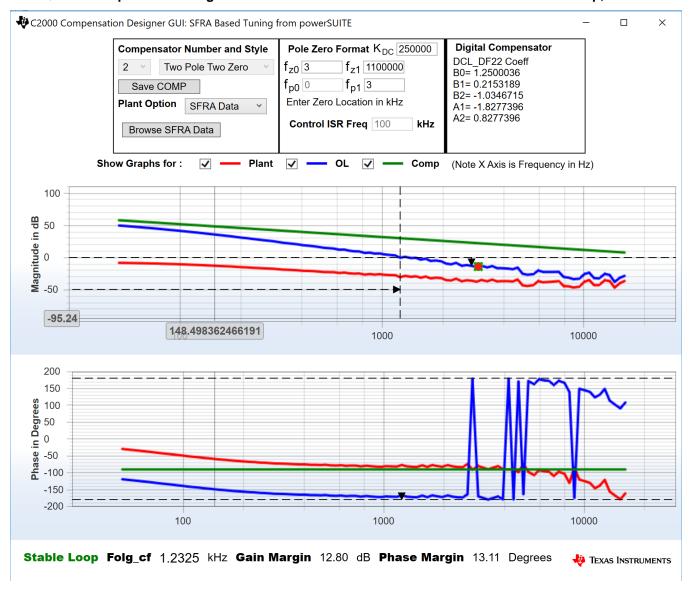

- 1. If using the powerSUITE page, go to step 2; otherwise, jump to step 8.

- 2. powerSUITE Settings: On the powerSUITE page,

- a. Select under the "Project Options" section "Lab 3: Closed Loop: Current" for the Lab.

- b. Under "Tuning", select SFRA to run on the current loop using the drop-down box. Save the page.

- 3. Under Control Loop Design, options for the current loop tuning will automatically be selected, Tuning  $\rightarrow$  Comp Number 2  $\rightarrow$  DF22.

- 4. Save the page by "Ctrl-S" and click on the Compensation Designer button

- 5. The compensation designer will then launch and prompt the user to select a valid SFRA data file. Import the SFRA data from the run in Lab 1 for the current loop, into the compensation designer to design a two-pole, two-zero compensator. It is good to keep more margins during this iteration of the design to ensure that when the loop is closed, the system is stable. Plant data from different runs of the SFRA can be checked to get a stable system under all conditions.

#### 图 50. Compensator Design With SFRA Based Plant Measurement for the Current Loop, Lab 3

- 注: The tuning is carried out in DF22 fashion; however, we run the DF13 in the software. This is done because soft-starting the DF13 is easier, whereas not possible with the DF22 structure. The coefficients in both cases remain the same. At the writing of this document, the DF12 structure is not available in DCL.

- 6. Once satisfied with the compensator design, click on "Save COMP". This will save the compensator values into the project.

- 7. Close the compensation designer, return to the powerSUITE page, and save ("Ctrl-S"). This will write the new compensator values to the "settings.h" file.

8. The following defines are set in the "settings.h" file for this build. These will be set by the powerSUITE page automatically; otherwise, edit the page manually.

```

#if CLLLC_LAB_NO == 3

#define CLLLC_INCR_BUILD 2

#define CLLLC_CONTROL_MODE CLLLC_CURRENT_MODE

// 0 means check with resistive load

#define CLLLC_SEC_CONNECTED_IN_BATTERY_EMULATION_MODE 0

#endif

#define CLLLC_SFRA_TYPE CLLLC_SFRA_CURRENT

```